Computer Systems: A Programmer's Perspective (3rd Edition)

3rd Edition

ISBN: 9780134092669

Author: Bryant, Randal E. Bryant, David R. O'Hallaron, David R., Randal E.; O'Hallaron, Bryant/O'hallaron

Publisher: PEARSON

expand_more

expand_more

format_list_bulleted

Textbook Question

Chapter 6, Problem 6.32HW

Repeat Problem 6.31 for memory address0x16E8

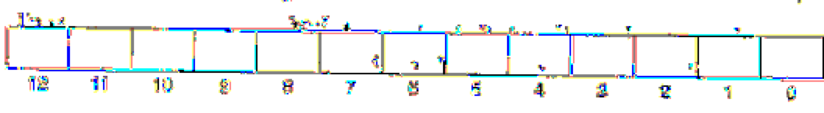

A. Address format (1 bit per box):

B. Memory Reference:

| Parameter | Value |

| Cache offset (CO) | 0x____ |

| Cache index (CI) | 0x____ |

| Cache tag (CT) | 0x____ |

| Cache hit? (Y/N) | ____ |

| Cache byte returned | 0x____ |

Expert Solution & Answer

Want to see the full answer?

Check out a sample textbook solution

Students have asked these similar questions

I need to define and discuss the uses of one monitoring or troubleshooting tool in Windows Server 2019. thank you

I would likr toget help with the following concepts:

- Windows Server features

- Windows Server versus Windows 10 used as a client-server network

I need to define and discuss the uses of one monitoring or troubleshooting tool in Windows Server 2019. thank you

Chapter 6 Solutions

Computer Systems: A Programmer's Perspective (3rd Edition)

Ch. 6.1 - Prob. 6.1PPCh. 6.1 - Prob. 6.2PPCh. 6.1 - Prob. 6.3PPCh. 6.1 - Prob. 6.4PPCh. 6.1 - Prob. 6.5PPCh. 6.1 - Prob. 6.6PPCh. 6.2 - Prob. 6.7PPCh. 6.2 - Prob. 6.8PPCh. 6.4 - Prob. 6.9PPCh. 6.4 - Prob. 6.10PP

Ch. 6.4 - Prob. 6.11PPCh. 6.4 - Prob. 6.12PPCh. 6.4 - Prob. 6.13PPCh. 6.4 - Prob. 6.14PPCh. 6.4 - Prob. 6.15PPCh. 6.4 - Prob. 6.16PPCh. 6.5 - Prob. 6.17PPCh. 6.5 - Prob. 6.18PPCh. 6.5 - Prob. 6.19PPCh. 6.5 - Prob. 6.20PPCh. 6.6 - Prob. 6.21PPCh. 6 - Prob. 6.22HWCh. 6 - Prob. 6.23HWCh. 6 - Suppose that a 2 MB file consisting of 512-byte...Ch. 6 - The following table gives the parameters for a...Ch. 6 - The following table gives the parameters for a...Ch. 6 - Prob. 6.27HWCh. 6 - This problem concerns the cache in Practice...Ch. 6 - Suppose we have a system with the following...Ch. 6 - Suppose we have a system with following...Ch. 6 - Suppose that a program using the cache in Problem...Ch. 6 - Repeat Problem 6.31 for memory address0x16E8 A....Ch. 6 - Prob. 6.33HWCh. 6 - Prob. 6.34HWCh. 6 - Prob. 6.35HWCh. 6 - Prob. 6.36HWCh. 6 - Prob. 6.37HWCh. 6 - Prob. 6.38HWCh. 6 - Prob. 6.39HWCh. 6 - Given the assumptions in Problem 6.38, determine...Ch. 6 - You are writing a new 3D game that you hope will...Ch. 6 - Prob. 6.42HWCh. 6 - Prob. 6.43HWCh. 6 - Prob. 6.45HWCh. 6 - Prob. 6.46HW

Additional Engineering Textbook Solutions

Find more solutions based on key concepts

The strain at point A on the bracket has components x = 300(106), y = 550(106), xy = 650(106), z = 0, Determine...

Mechanics of Materials (10th Edition)

Explain the meaning of the term object persistence.

Database Concepts (8th Edition)

In Exercises 33 through 40, determine the output displayed in the list box by the lines of code. DimtotalOunces...

Introduction To Programming Using Visual Basic (11th Edition)

Write an input validation loop that asks the user to enter a number in the range of 1 through 4,

Starting Out with Java: From Control Structures through Data Structures (4th Edition) (What's New in Computer Science)

What is the disadvantage of having too many features in a language?

Concepts Of Programming Languages

What is the output of this loop? Comment on the code. int n = 1024; int log = 0; for (int i = 1; i n; i = i 2...

Problem Solving with C++ (10th Edition)

Knowledge Booster

Learn more about

Need a deep-dive on the concept behind this application? Look no further. Learn more about this topic, computer-science and related others by exploring similar questions and additional content below.Similar questions

- Please solve and answer the questions correctly please. Thank you!!arrow_forwardConsidering the TM example of binary sum ( see attached)do the step-by-step of execution for the binary numbers 1101 and 11. Feel free to use the Formal Language Editor Tool to execute it; Write it down the current state of the tape (including the head position) and indicate the current state of the TM at each step.arrow_forwardI need help on inculding additonal code where I can can do the opposite code of MatLab, where the function of t that I enter becomes the result of F(t), in other words, turning the time-domain f(t) into the frequency-domain function F(s):arrow_forward

arrow_back_ios

SEE MORE QUESTIONS

arrow_forward_ios

Recommended textbooks for you

Systems ArchitectureComputer ScienceISBN:9781305080195Author:Stephen D. BurdPublisher:Cengage Learning

Systems ArchitectureComputer ScienceISBN:9781305080195Author:Stephen D. BurdPublisher:Cengage Learning C++ for Engineers and ScientistsComputer ScienceISBN:9781133187844Author:Bronson, Gary J.Publisher:Course Technology Ptr

C++ for Engineers and ScientistsComputer ScienceISBN:9781133187844Author:Bronson, Gary J.Publisher:Course Technology Ptr Principles of Information Systems (MindTap Course...Computer ScienceISBN:9781305971776Author:Ralph Stair, George ReynoldsPublisher:Cengage Learning

Principles of Information Systems (MindTap Course...Computer ScienceISBN:9781305971776Author:Ralph Stair, George ReynoldsPublisher:Cengage Learning C++ Programming: From Problem Analysis to Program...Computer ScienceISBN:9781337102087Author:D. S. MalikPublisher:Cengage Learning

C++ Programming: From Problem Analysis to Program...Computer ScienceISBN:9781337102087Author:D. S. MalikPublisher:Cengage Learning Database Systems: Design, Implementation, & Manag...Computer ScienceISBN:9781305627482Author:Carlos Coronel, Steven MorrisPublisher:Cengage Learning

Database Systems: Design, Implementation, & Manag...Computer ScienceISBN:9781305627482Author:Carlos Coronel, Steven MorrisPublisher:Cengage Learning Enhanced Discovering Computers 2017 (Shelly Cashm...Computer ScienceISBN:9781305657458Author:Misty E. Vermaat, Susan L. Sebok, Steven M. Freund, Mark Frydenberg, Jennifer T. CampbellPublisher:Cengage Learning

Enhanced Discovering Computers 2017 (Shelly Cashm...Computer ScienceISBN:9781305657458Author:Misty E. Vermaat, Susan L. Sebok, Steven M. Freund, Mark Frydenberg, Jennifer T. CampbellPublisher:Cengage Learning

Systems Architecture

Computer Science

ISBN:9781305080195

Author:Stephen D. Burd

Publisher:Cengage Learning

C++ for Engineers and Scientists

Computer Science

ISBN:9781133187844

Author:Bronson, Gary J.

Publisher:Course Technology Ptr

Principles of Information Systems (MindTap Course...

Computer Science

ISBN:9781305971776

Author:Ralph Stair, George Reynolds

Publisher:Cengage Learning

C++ Programming: From Problem Analysis to Program...

Computer Science

ISBN:9781337102087

Author:D. S. Malik

Publisher:Cengage Learning

Database Systems: Design, Implementation, & Manag...

Computer Science

ISBN:9781305627482

Author:Carlos Coronel, Steven Morris

Publisher:Cengage Learning

Enhanced Discovering Computers 2017 (Shelly Cashm...

Computer Science

ISBN:9781305657458

Author:Misty E. Vermaat, Susan L. Sebok, Steven M. Freund, Mark Frydenberg, Jennifer T. Campbell

Publisher:Cengage Learning

Instruction Format (With reference to address); Author: ChiragBhalodia;https://www.youtube.com/watch?v=lNdy8HREvgo;License: Standard YouTube License, CC-BY