Concept explainers

The two-port networks of Fig. 16.50 are connected in series. (a) Determine the impedance parameters for the series connection by first finding the z parameters of the individual networks. (b) If the two networks are instead connected in parallel, determine the admittance parameters of the combination by first finding the y parameters of the individual networks. (c) Verify your answer to part (b) by using Table 16.1 in conjunction with your answer to part (a).

(a)

The value of impedance parameters for the given condition.

Answer to Problem 35E

The value of total impedance when the two port networks are connected in series is

Explanation of Solution

Given data:

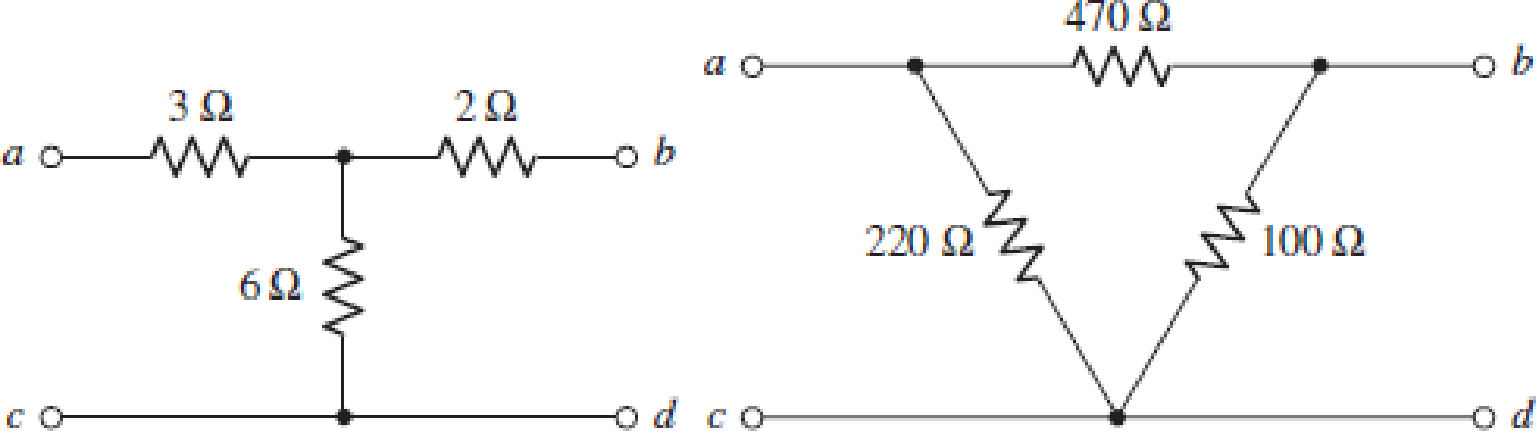

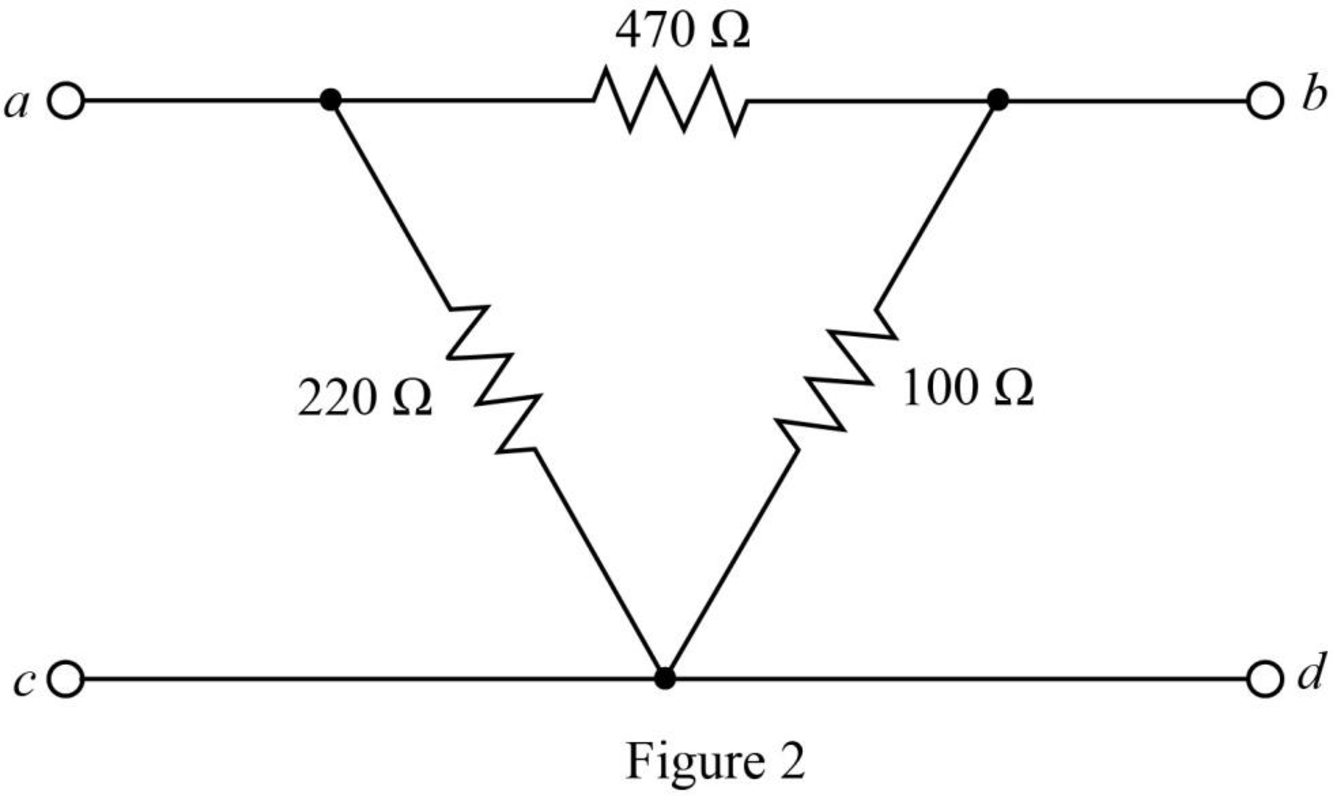

The given diagram is shown in Figure 1.

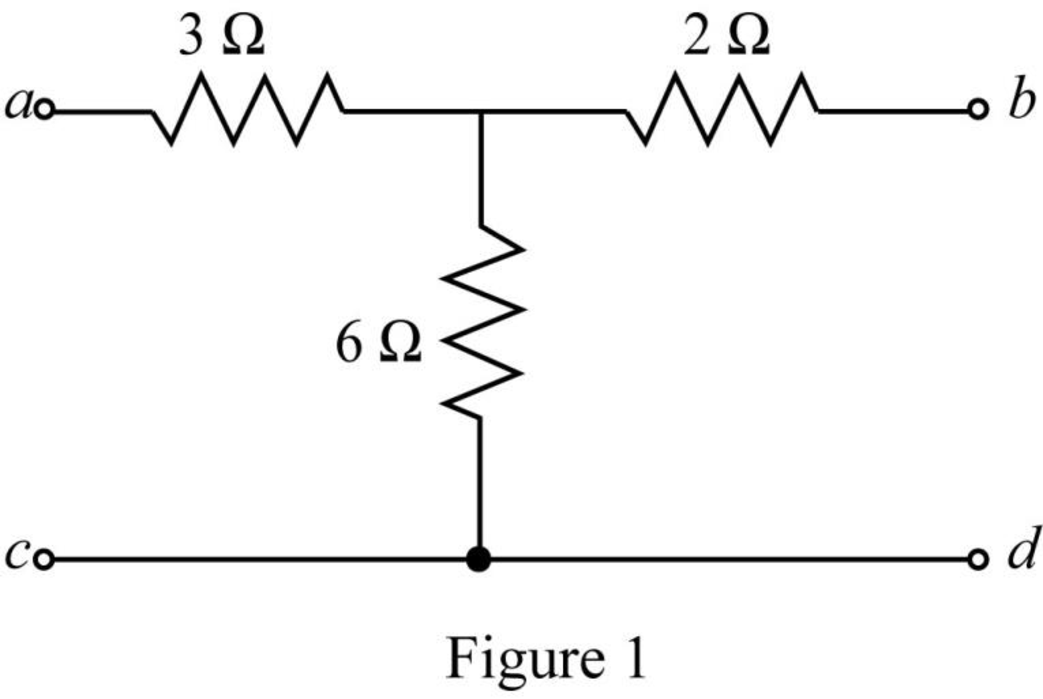

The given diagram is shown in Figure 2.

Calculation:

Determine the impedance parameter

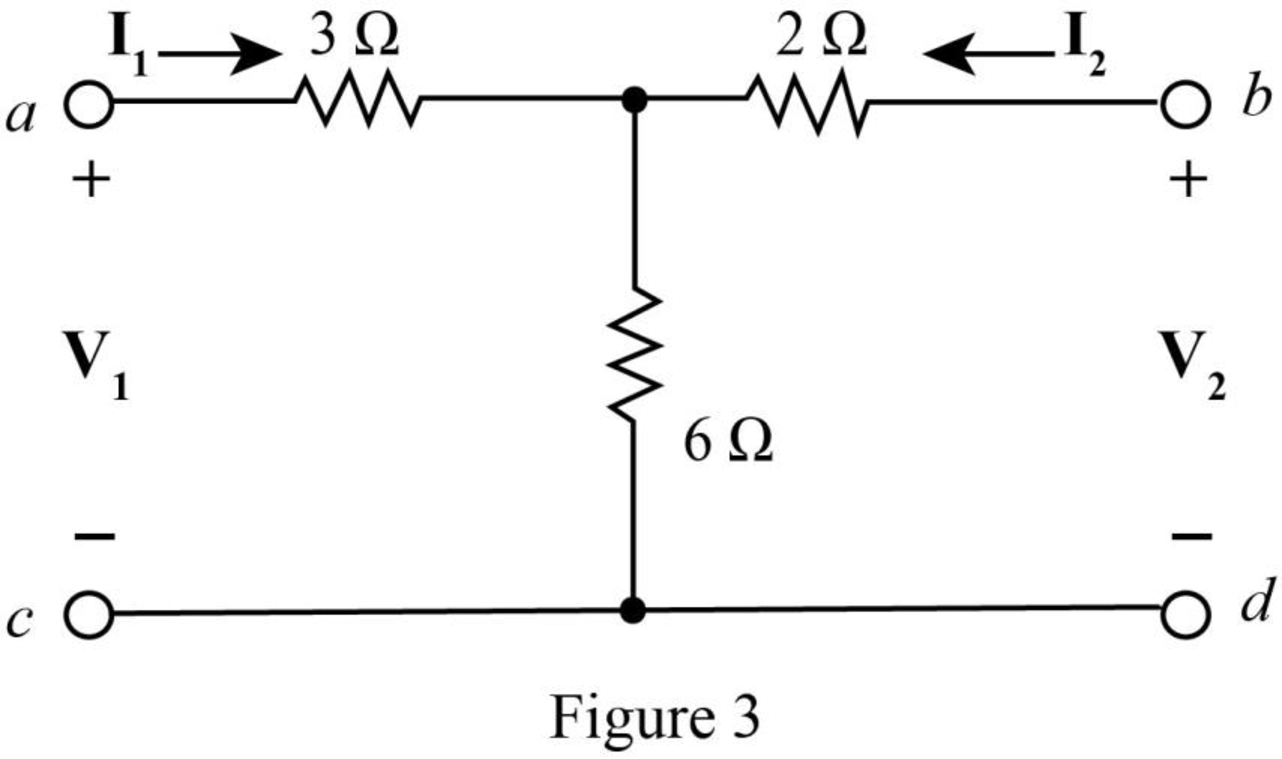

The required diagram is shown in Figure 3.

The impedance parameters can be expressed as,

Substitute

Substitute

Substitute

Substitute

Apply KVL left loop of Figure 3.

Substitute

Substitute

Substitute

Substitute

Apply KVL at the right loop.

Substitute

Substitute

Substitute

Substitute

Hence the

Convert the delta connected network to star connected network.

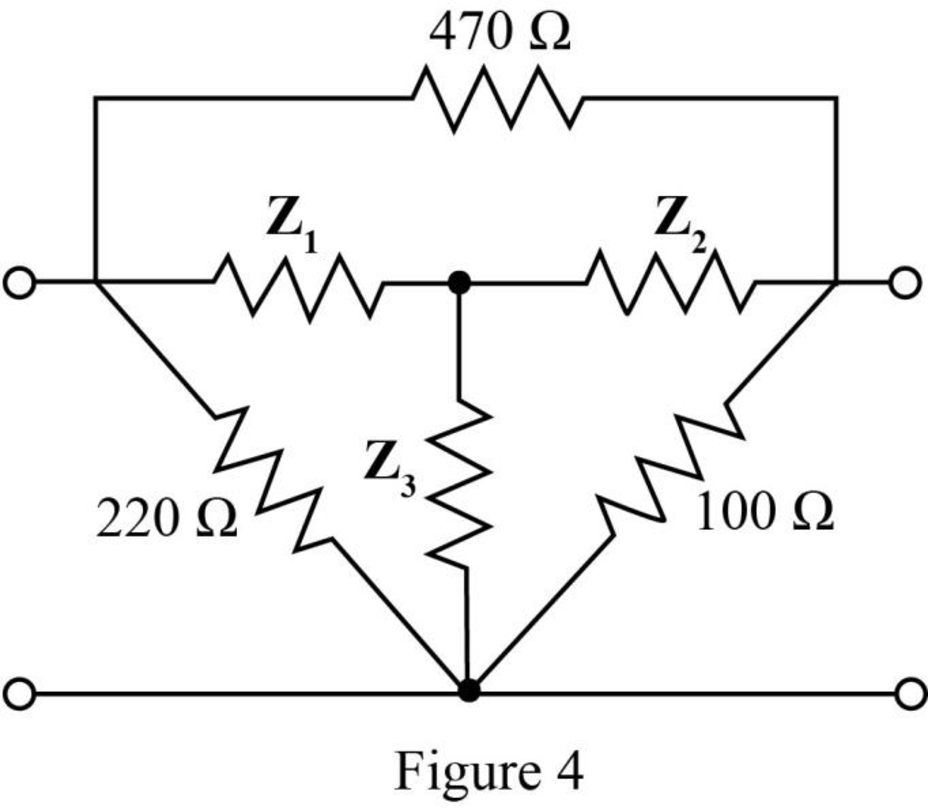

The required diagram is shown in Figure 4.

The impedance

The impedance

The impedance

Redraw the star connected circuit.

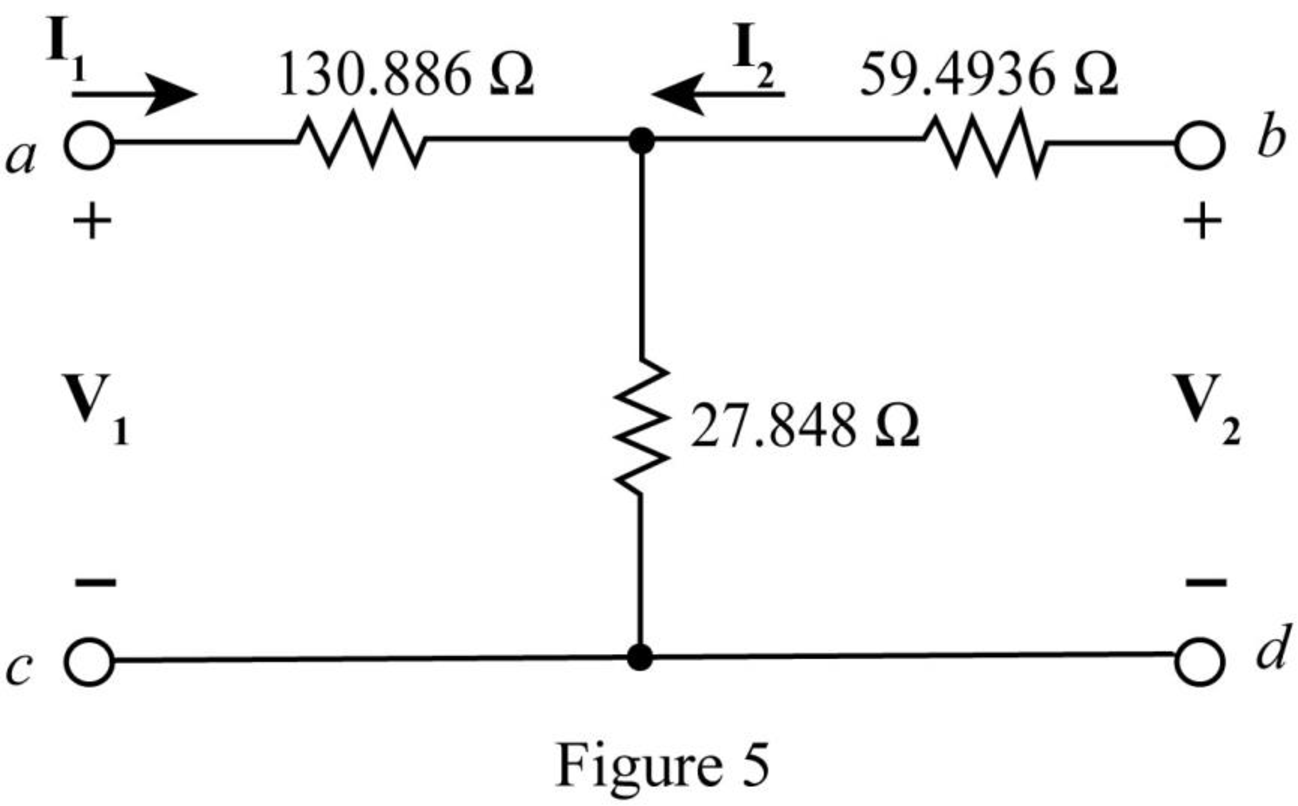

The required diagram is shown in Figure 5.

Apply KVL in the left loop.

Substitute

Substitute

Substitute

Substitute

Apply KVL at right loop of Figure 5.

Substitute

Substitute

Substitute

Substitute

The

The overall impedance matrix when the two port networks are connected in series is,

Substitute

Conclusion:

Therefore, the value of total impedance when the two port networks are connected in series is

(b)

The value of admittance parameters for the given condition.

Answer to Problem 35E

The value of total admittance when the two port networks are connected in parallel is

Explanation of Solution

Calculation:

The standard equation for admittance parameters is given by,

Substitute

Substitute

Substitute

Substitute

Modify the given diagram for

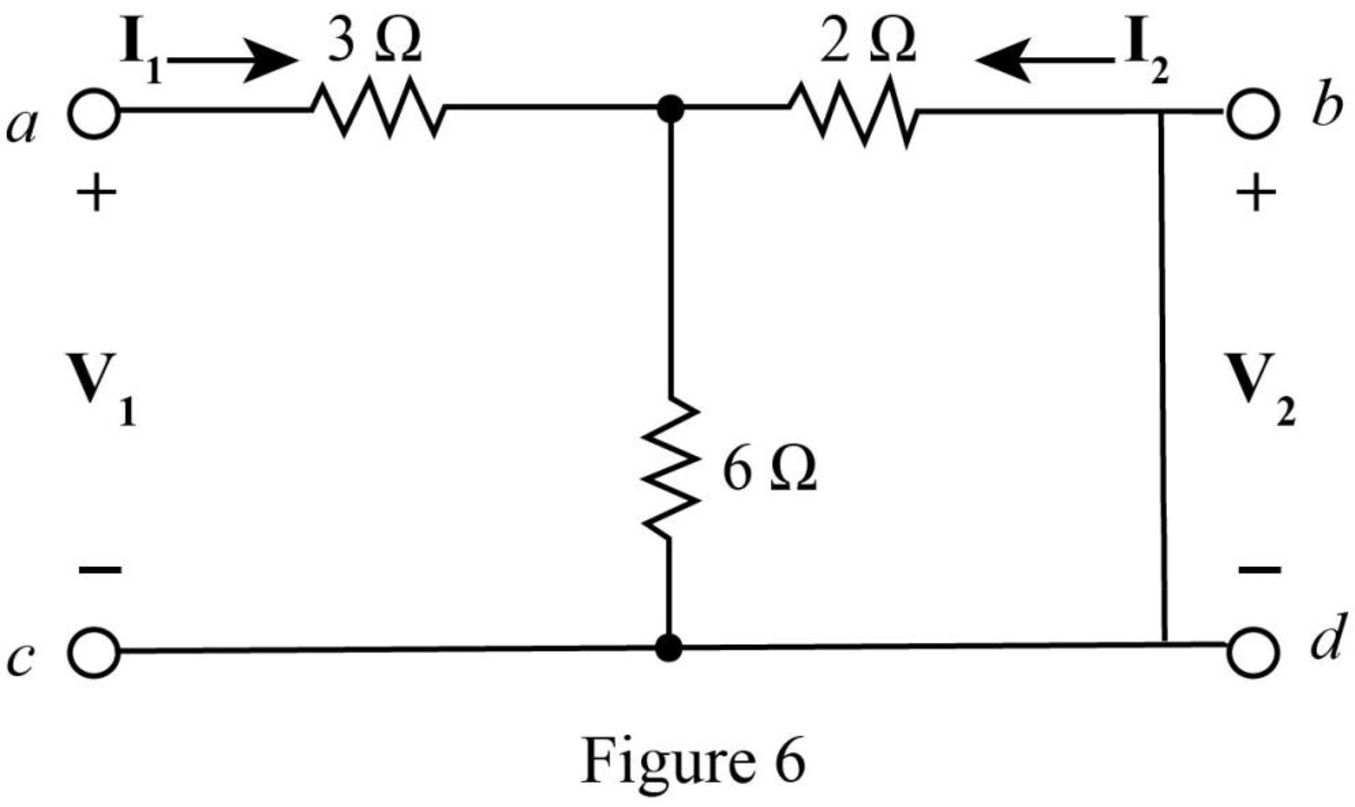

The required diagram is shown in Figure 6.

The resistances

The equivalent resistance is,

Further, the resistances

The total equivalent resistance of the circuit is given by,

Substitute

The input voltage calculated from the circuit is written as,

Rearrange the above equation as,

Substitute

Substitute

Rearrange equation (7) as,

Apply current division rule in Figure 6.

Substitute

Substitute

Modify the given diagram for

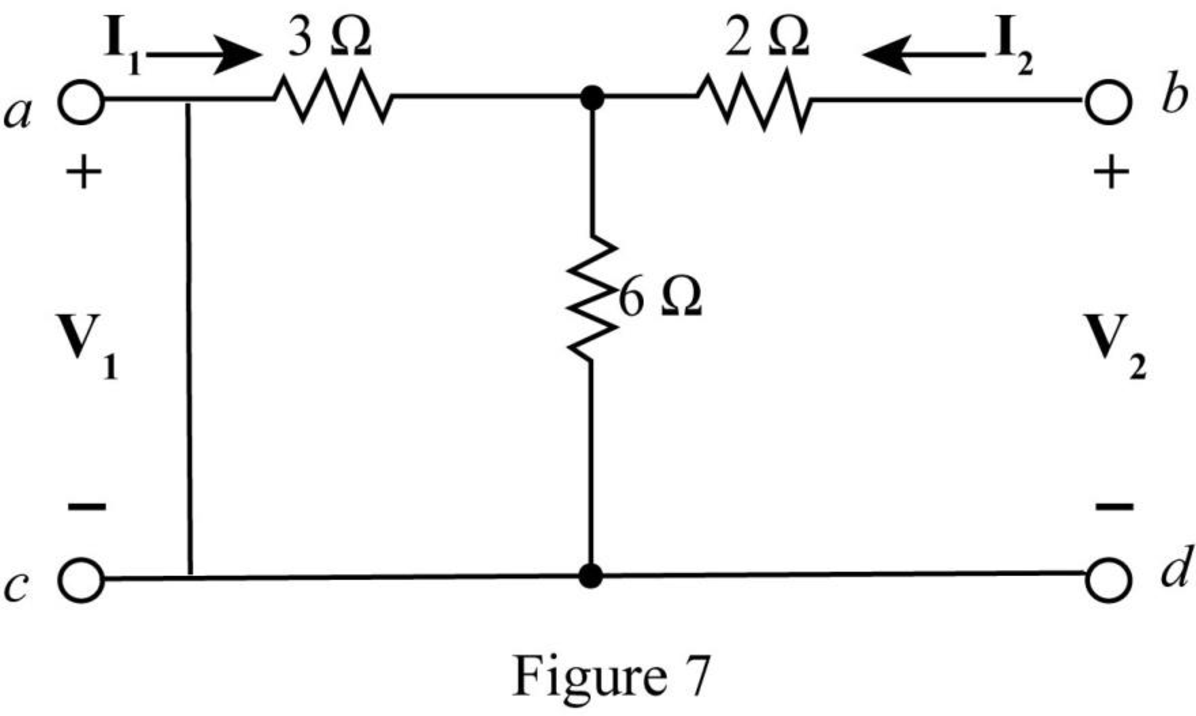

The required diagram is shown in Figure 7.

Rearrange equation (8).

Apply current division rule in the circuit of Figure 7.

Substitute

Substitute

The resistances

The equivalent resistance is,

Further, the resistances

The total equivalent resistance of the circuit is given by,

Substitute

The input voltage of Figure 7 can be expressed as,

Rearrange the above equation as,

Substitute

Substitute

The

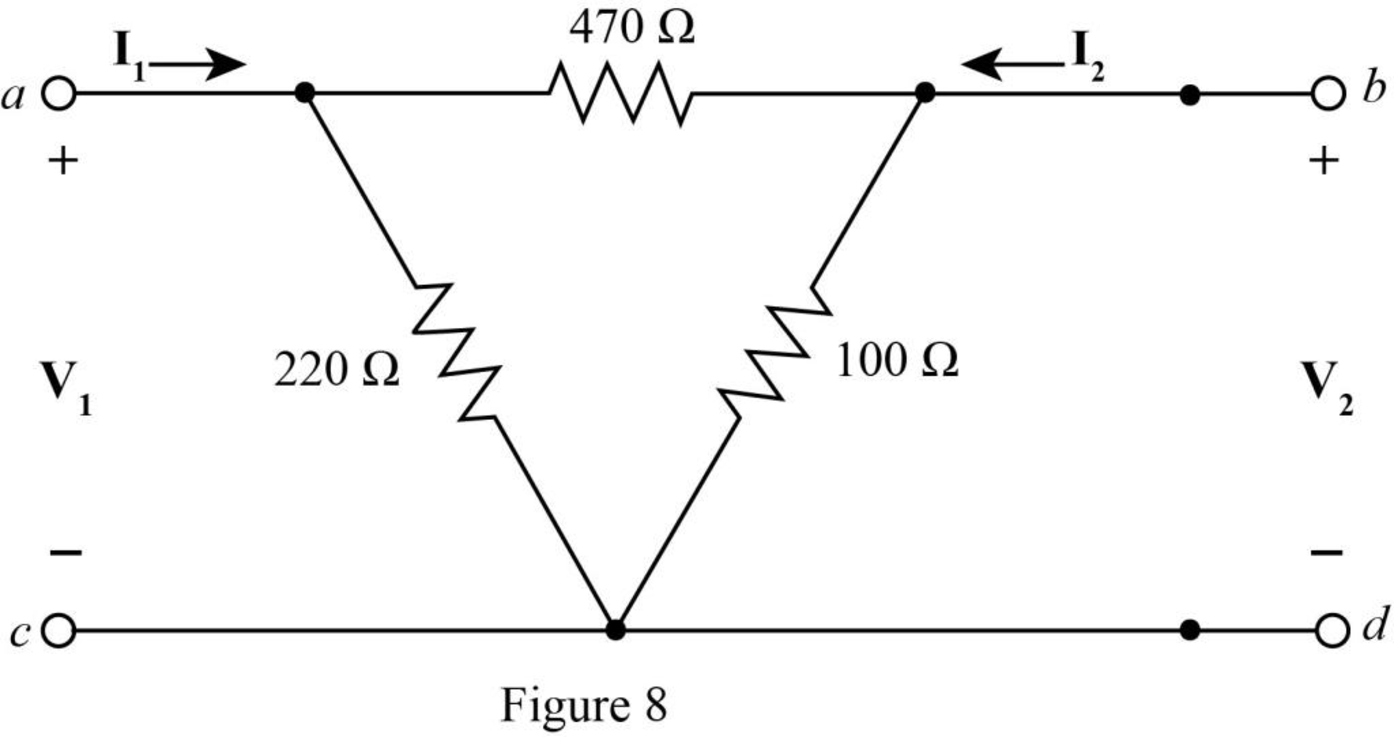

Redraw the Figure 2 and show the input voltage

The required diagram is shown in Figure 8.

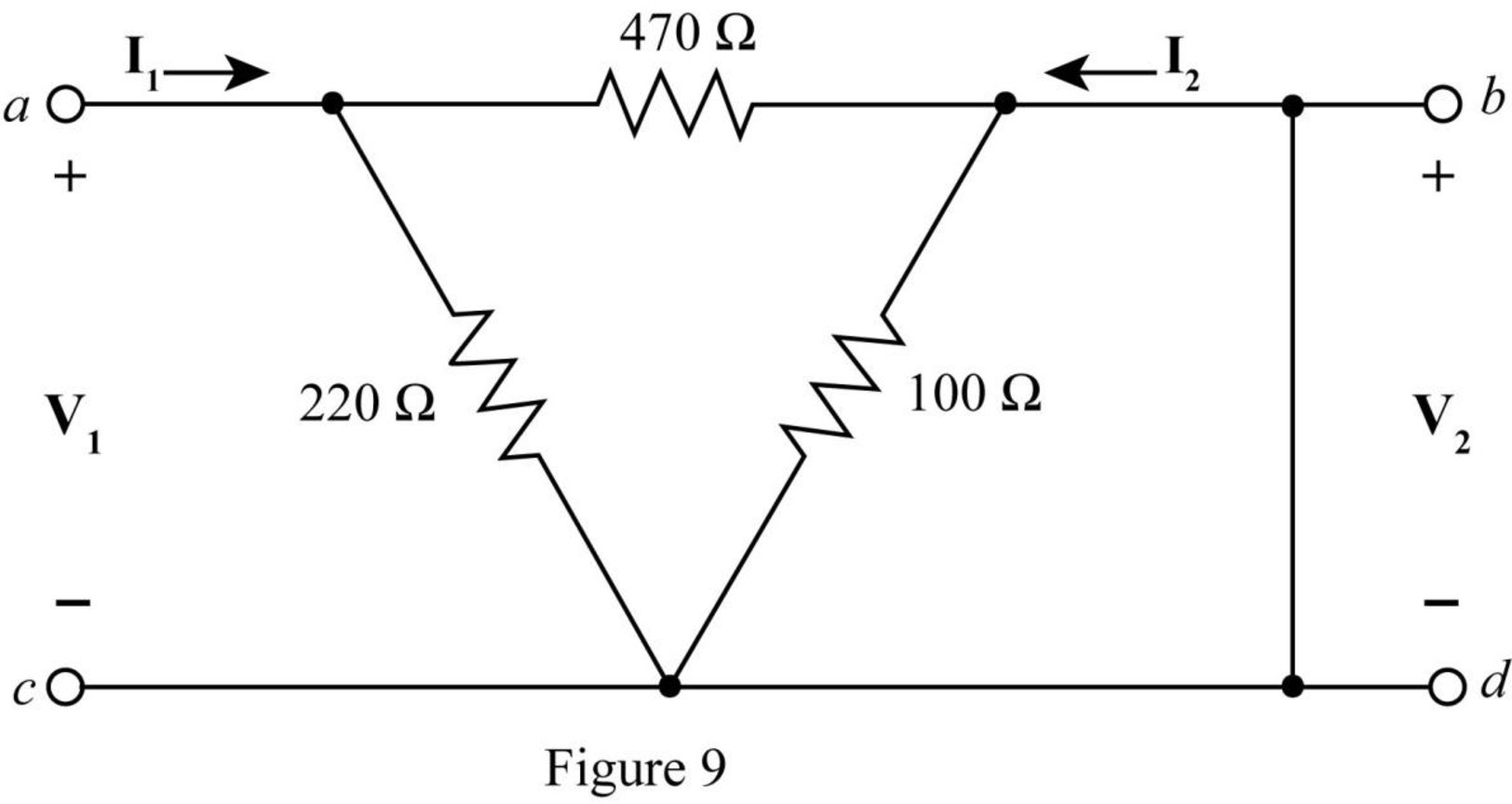

Redraw the above figure for

The required diagram is shown in Figure 9.

The

Therefore,

The equivalent resistance of the above circuit is,

The input voltage of Figure 9 can be expressed as,

Rearrange the above equation as,

Substitute

Substitute

The voltage across

Therefore, the current through

Rearrange the above equation as,

Substitute

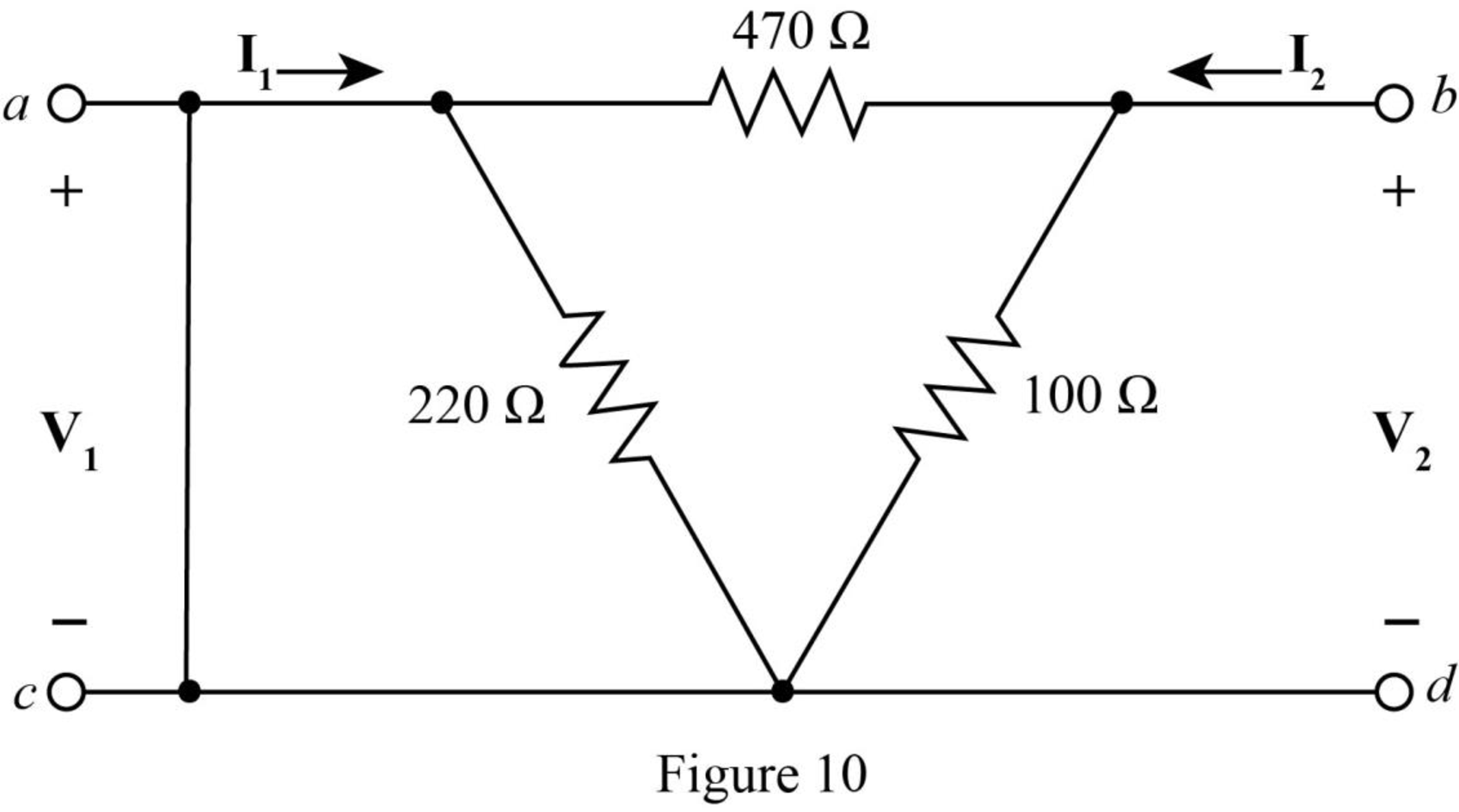

Redraw the above figure for

The required diagram is shown in Figure 10.

The

The voltage across

Therefore, the current through

Rearrange the above equation as,

Substitute

The

The equivalent resistance of the above circuit is,

The input voltage of Figure 10 can be expressed as,

Rearrange the above equation as,

Substitute

Substitute

The

The overall admittance matrix when the two port networks are connected in parallel is,

Substitute

Conclusion:

Therefore, the value of total admittance when the two port networks are connected in parallel is

(c)

The value of

Explanation of Solution

Calculation:

The determinant of

The matrix for

Substitute

The determinant of

Substitute

Conclusion:

Therefore, the value of

Want to see more full solutions like this?

Chapter 16 Solutions

Loose Leaf for Engineering Circuit Analysis Format: Loose-leaf

Additional Engineering Textbook Solutions

Database Concepts (8th Edition)

Electric Circuits. (11th Edition)

Thermodynamics: An Engineering Approach

Starting Out with C++: Early Objects (9th Edition)

Starting Out with Java: From Control Structures through Data Structures (4th Edition) (What's New in Computer Science)

Introduction To Programming Using Visual Basic (11th Edition)

- Please solve in detailarrow_forward6.7 The transmitting aerial shown in Fig. Q.3 is supplied with current at 80 A peak and at frequency 666.66 kHz. Calculate (a) the effective height of the aerial, and (b) the electric field strength produced at ground level 40 km away. 60 m Fig. Q.3 Input 48 m Eartharrow_forwardox SIM 12.11 Consider the class B output stage, using MOSFETs, shown in Fig. P12.11. Let the devices have |V|= 0.5 V and μC WIL = 2 mA/V². With a 10-kHz sine-wave input of 5-V peak and a high value of load resistance, what peak output would you expect? What fraction of the sine-wave period does the crossover interval represent? For what value of load resistor is the peak output voltage reduced to half the input? Figure P12.11 +5 V Q1 Q2 -5Varrow_forward

- 4 H ་་་་་་་ 四一周 A H₂ Find out put c I writ R as a function G, H, Harrow_forward4 H A H₂ 四一周 Find out put c I writ R as a function G, H, Harrow_forward8. (a) In a Round-Robin tournament, the Tigers beat the Blue Jays, the Tigers beat the Cardinals, the Tigers beat the Orioles, the Blue Jays beat the Cardinals, the Blue Jays beat the Orioles and the Cardinals beat the Orioles. Model this outcome with a directed graph. https://www.akubihar.com (b) (c) ✓ - Let G = (V, E) be a simple graph. Let R be the relation on V consisting of pairs of vertices (u, v) such that there is a path from u to vor such that u= v. Show that R is an equivalence relation. 3 3 Determine whether the following given pair of directed graphs, shown in Fig. 1 and Fig. 2, are isomorphic or not. Exhibit an isomorphism or provide a rigorous argument that none exists. 4+4=8 Աշ աշ ИНИЯ Fig. 1 Fig. 2 Querarrow_forward

- EXAMPLE 4.5 Objective: Determine ID, circuit. V SG' SD Vs and the small - signal voltage gain of a PMOS transistor Consider the circuit shown in Figure 4.20(a). The transistor parameters are A K = 0.80m- V Р _2’TP = 0.5V, and λ = 0 Varrow_forwardNeed a solution and don't use chatgptarrow_forwardNeed a solarrow_forward

Power System Analysis and Design (MindTap Course ...Electrical EngineeringISBN:9781305632134Author:J. Duncan Glover, Thomas Overbye, Mulukutla S. SarmaPublisher:Cengage Learning

Power System Analysis and Design (MindTap Course ...Electrical EngineeringISBN:9781305632134Author:J. Duncan Glover, Thomas Overbye, Mulukutla S. SarmaPublisher:Cengage Learning