Concept explainers

To plot: The graphof

To find: The value of

Answer to Problem 16.79P

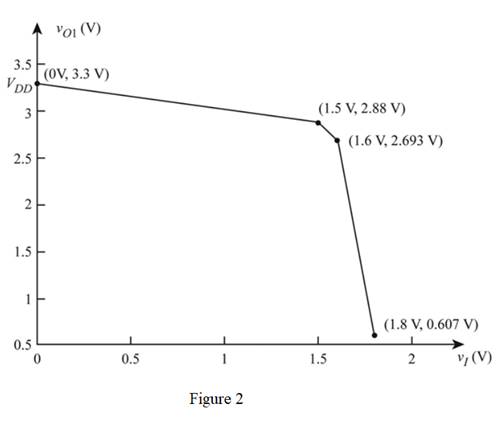

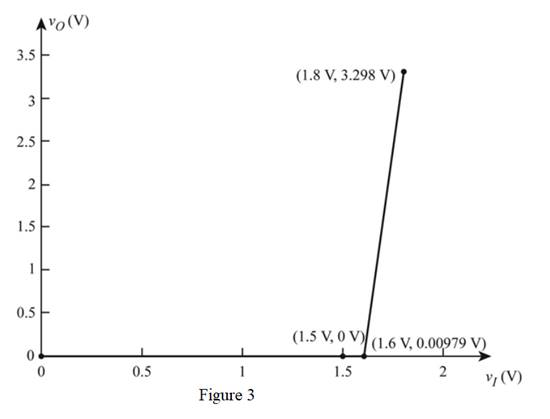

The required plots are shown in Figure 2 and Figure 3. The value of the voltage

Explanation of Solution

Given:

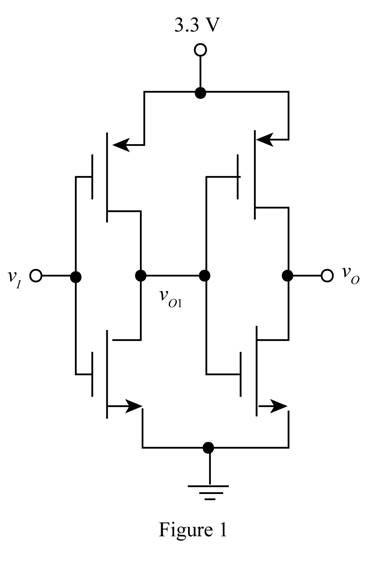

The given diagram is shown in Figure 1.

Calculation:

The expression to determine the transition points

Substitute

Case(i)

The expression to determine the output voltage of the first CMOS inverter is given by,

Substitute

The expression to determine the output voltage of the second CMOS inverter is given by,

Substitute

Thus the value of the of appropriate voltage is

Case (ii)

The expression to determine the output voltage of the first CMOS inverter is given by,

Substitute

The bias voltage is

The expression to determine the output voltage of the second CMOS inverter is given by,

Substitute

Thus the value of the of appropriate voltage is

Case (iii)

The expression to determine the output voltage of the first CMOS inverter is given by,

Substitute

The bias voltage is

The expression to determine the output voltage of the second CMOS inverter is given by,

Substitute

Thus the value of the of appropriate voltage is

Case (iv)

The output voltage of the first and the second CMOS inverter is switching point when the input voltage is the

The plot for the voltage between

The plot between the second CMOS inviter output

The required plot is shown in Figure 3

Conclusion:

Therefore, the required plots are shown in Figure 2 and Figure 3. The value of the voltage

Want to see more full solutions like this?

Chapter 16 Solutions

MICROELECT. CIRCUIT ANALYSIS&DESIGN (LL)

- Show all the steps please, Solve for the current through R2 if E2 is replaced by a current source of 10mA using superposition theorem. R5=470Ω R2=1000Ω R6=820Ωarrow_forwardPlease solve it by explaining the steps. I am trying to prepare for my exam tomorrow, so any tips and tricks to solve similar problems are highly appreciated. Plus, this is a past exam I am using to prepare.arrow_forwardPlease solve it by explaining the steps. I am trying to prepare for my exam today, so any tips and tricks to solve similar problems are highly appreciated. Plus, this is a past exam I am using to prepare.arrow_forward

- If C is the circle |z|=4 evaluate f f (z)dz for each of the following functions using residue. 1 f(z) = z(z²+6z+4)arrow_forwardIf C is the circle |z|=4 evaluate ff(z)dz for each of the following functions using residue. f(z) z(z²+6z+4)arrow_forwardDetermine X(w) for the given function shown in Figure (1) by applying the differentiation property of the Fourier Transform. 1 x(t) Figure (1) -2 I -1 1 2arrow_forward

- Please solve it by explaining the steps. I am trying to prepare for my exam tomorrow, so any tips and tricks to solve similar problems are highly appreciated. Plus, this is a past exam I am using to prepare.arrow_forwardPlease solve it by explaining the steps. I am trying to prepare for my exam tomorrow, so any tips and tricks to solve similar problems are highly appreciated. Plus, this is a past exam I am using to prepare.arrow_forwardPlease solve it by explaining the steps. I am trying to prepare for my exam tomorrow, so any tips and tricks to solve similar problems are highly appreciated. Plus, this is a past exam I am using to prepare.arrow_forward

- Please solve it by explaining the steps. I am trying to prepare for my exam tomorrow, so any tips and tricks to solve similar problems are highly appreciated. Plus, this is a past exam I am using to prepare.arrow_forwardPlease solve it by explaining the steps. I am trying to prepare for my exam tomorrow, so any tips and tricks to solve similar problems are highly appreciated. Plus, this is a past exam I am using to prepare.arrow_forwardPlease solve it by explaining the steps. I am trying to prepare for my exam tomorrow, so any tips and tricks to solve similar problems are highly appreciated. Plus, this is a past exam I am using to prepare.arrow_forward

Introductory Circuit Analysis (13th Edition)Electrical EngineeringISBN:9780133923605Author:Robert L. BoylestadPublisher:PEARSON

Introductory Circuit Analysis (13th Edition)Electrical EngineeringISBN:9780133923605Author:Robert L. BoylestadPublisher:PEARSON Delmar's Standard Textbook Of ElectricityElectrical EngineeringISBN:9781337900348Author:Stephen L. HermanPublisher:Cengage Learning

Delmar's Standard Textbook Of ElectricityElectrical EngineeringISBN:9781337900348Author:Stephen L. HermanPublisher:Cengage Learning Programmable Logic ControllersElectrical EngineeringISBN:9780073373843Author:Frank D. PetruzellaPublisher:McGraw-Hill Education

Programmable Logic ControllersElectrical EngineeringISBN:9780073373843Author:Frank D. PetruzellaPublisher:McGraw-Hill Education Fundamentals of Electric CircuitsElectrical EngineeringISBN:9780078028229Author:Charles K Alexander, Matthew SadikuPublisher:McGraw-Hill Education

Fundamentals of Electric CircuitsElectrical EngineeringISBN:9780078028229Author:Charles K Alexander, Matthew SadikuPublisher:McGraw-Hill Education Electric Circuits. (11th Edition)Electrical EngineeringISBN:9780134746968Author:James W. Nilsson, Susan RiedelPublisher:PEARSON

Electric Circuits. (11th Edition)Electrical EngineeringISBN:9780134746968Author:James W. Nilsson, Susan RiedelPublisher:PEARSON Engineering ElectromagneticsElectrical EngineeringISBN:9780078028151Author:Hayt, William H. (william Hart), Jr, BUCK, John A.Publisher:Mcgraw-hill Education,

Engineering ElectromagneticsElectrical EngineeringISBN:9780078028151Author:Hayt, William H. (william Hart), Jr, BUCK, John A.Publisher:Mcgraw-hill Education,