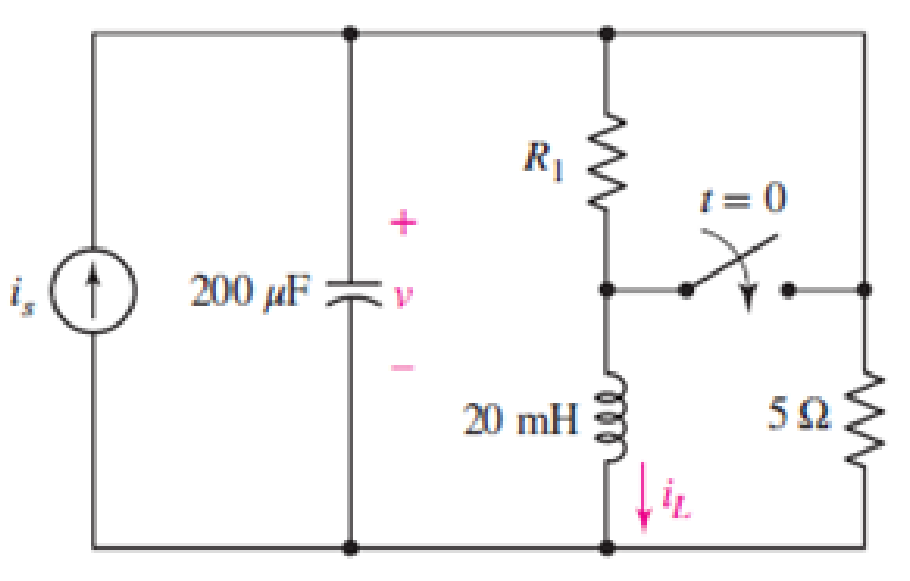

For the circuit of Fig. 9.45, is(t) = 30u(−t) mA. (a) Select R1 so that v(0+) = 6 V. (b) Compute v(2 ms). (c) Determine the settling time of the capacitor voltage. (d) Is the inductor current settling time the same as your answer to part (c)?

FIGURE 9.45

(a)

Select

Answer to Problem 26E

The resistance

Explanation of Solution

Given Data:

Formula used:

The expression for the exponential damping coefficient or the neper frequency is as follows:

Here,

The expression for the resonant frequency is as follows:

Here,

The expression for a critically damped response of a source free parallel RLC circuit is as follows:

Here,

Calculation:

The unit-step forcing function as a function of time which is zero for all values of its argument less than zero and which is unity for all positive values of its argument.

Here,

So, at

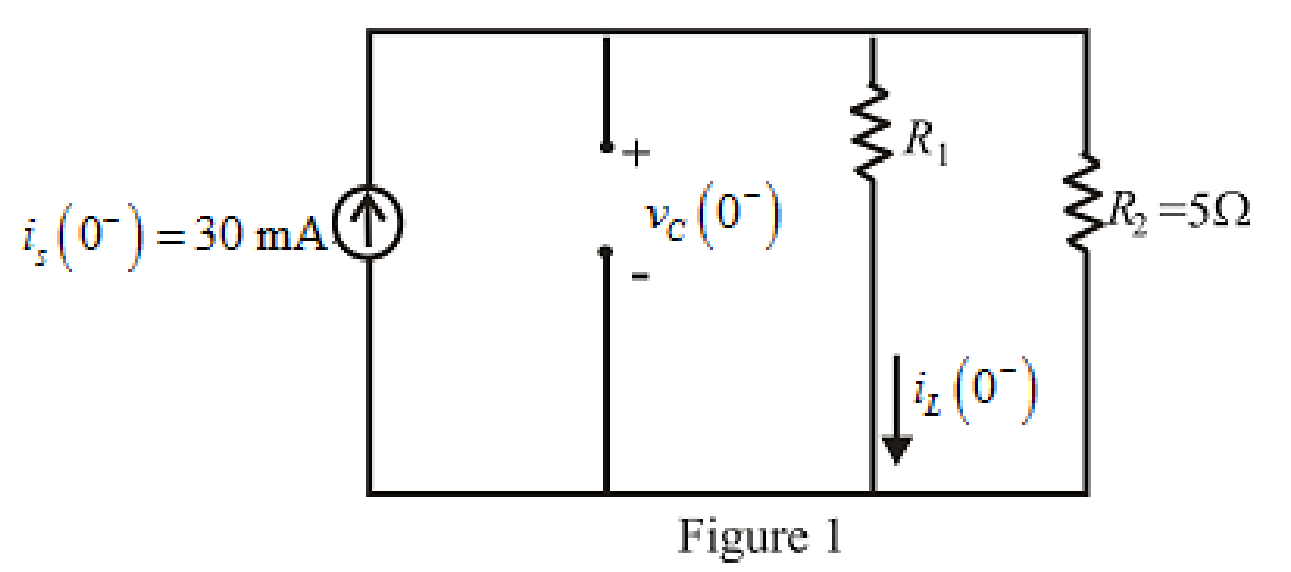

The redrawn circuit diagram is given in Figure 1 at

Refer to the redrawn Figure 1:

The expression for the current through the inductor at

Here,

The expression for the voltage across the capacitor at

Here,

Substitute

The capacitor does not allow sudden change in the voltage, so,

The voltage across the capacitor at

Substitute

Rearrange for

The resistance cannot be negative so, the resistance

Conclusion:

Thus, the resistance

(b)

Compute

Answer to Problem 26E

The value of the voltage

Explanation of Solution

Given data:

The time is

Calculation:

Substitute

The inductor does not allow sudden change in the current.

So,

So the current through inductor at

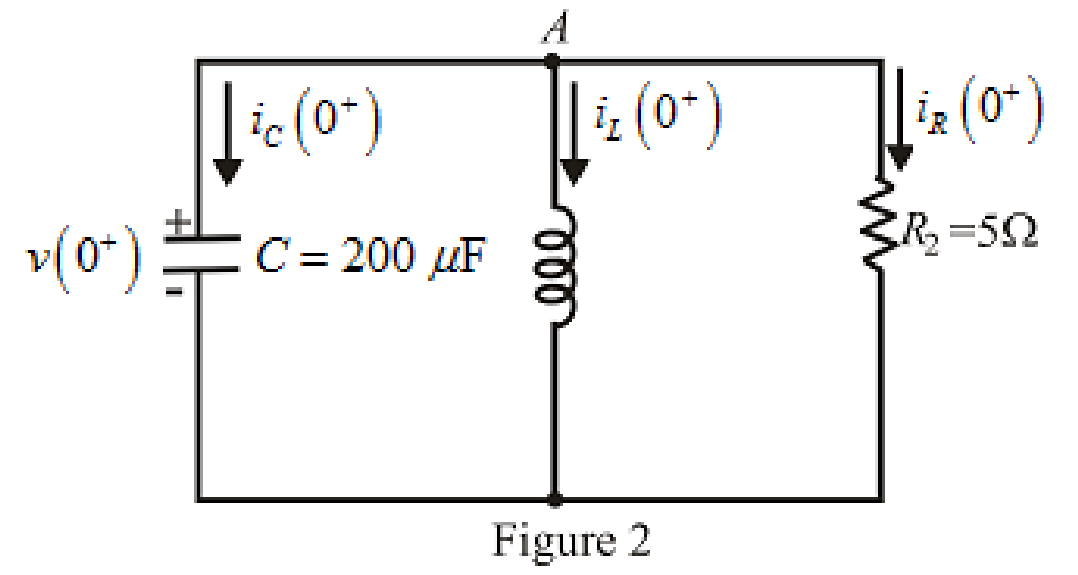

The redrawn circuit diagram is given in Figure 2 at

Refer to the redrawn Figure 2:

The expression for the current flowing in the

Here,

Substitute

Apply KCL at node

Here,

Substitute

Rearrange for

Substitute

Substitute

Substitute

Substitute

The voltage across the capacitor at

Substitute

Rearrange for

The expression for the current flowing through the

Substitute

Rearrange for

Substitute

The current flowing through the

Substitute

Substitute

Rearrange for

Substitute

Substitute

Conclusion:

Thus, the value of the voltage

(c)

Determine the settling time of the capacitor voltage.

Answer to Problem 26E

The settling time of the capacitor voltage is

Explanation of Solution

Calculation:

The maximum voltage appears across the capacitor at

So, for maximum voltage,

Substitute

Settling time is the time at which the value of the voltage reaches

The expression for the voltage at

Here,

Substitute

Substitute

The value of

Conclusion:

Thus, the settling time of the capacitor voltage is

(d)

Is the inductor current settling time the same as your answer to part (c)?

Answer to Problem 26E

The inductor current settling time is not same as capacitor voltage settling time.

Explanation of Solution

Calculation:

The expression for the current through inductor is as follows:

Here,

Substitute

Simplify further.

The maximum current through the inductor is at

So, for the maximum current,

Substitute

Settling time is the time at which the value of the current reaches

The expression for the current at

Here,

Substitute

Substitute

Rearrange equation (22).

The value of

So the inductor current settling time is

Conclusion:

Thus, the inductor current settling time is not same as capacitor settling time.

Want to see more full solutions like this?

Chapter 9 Solutions

Loose Leaf for Engineering Circuit Analysis Format: Loose-leaf

- 4 H ་་་་་་་ 四一周 A H₂ Find out put c I writ R as a function G, H, Harrow_forward4 H A H₂ 四一周 Find out put c I writ R as a function G, H, Harrow_forward8. (a) In a Round-Robin tournament, the Tigers beat the Blue Jays, the Tigers beat the Cardinals, the Tigers beat the Orioles, the Blue Jays beat the Cardinals, the Blue Jays beat the Orioles and the Cardinals beat the Orioles. Model this outcome with a directed graph. https://www.akubihar.com (b) (c) ✓ - Let G = (V, E) be a simple graph. Let R be the relation on V consisting of pairs of vertices (u, v) such that there is a path from u to vor such that u= v. Show that R is an equivalence relation. 3 3 Determine whether the following given pair of directed graphs, shown in Fig. 1 and Fig. 2, are isomorphic or not. Exhibit an isomorphism or provide a rigorous argument that none exists. 4+4=8 Աշ աշ ИНИЯ Fig. 1 Fig. 2 Querarrow_forward

- EXAMPLE 4.5 Objective: Determine ID, circuit. V SG' SD Vs and the small - signal voltage gain of a PMOS transistor Consider the circuit shown in Figure 4.20(a). The transistor parameters are A K = 0.80m- V Р _2’TP = 0.5V, and λ = 0 Varrow_forwardNeed a solution and don't use chatgptarrow_forwardNeed a solarrow_forward

- Do not use chaarrow_forwardIn the following table, the value of 40 resistors are recorded in ohms. (a) Construct the frequency distribution table using number of class=5. (b) Plot the histogram of frequency table. 45 50 61 32 25 50 64 28 40 40 46 47 48 35 58 35 54 38 68 76 19 63 26 65 54 42 68 47 53 36 73 44 49 35 38 42 56 44 45 57arrow_forwardcircuit source transformation step by step v0 findarrow_forward

- Find Laplace transform and the corresponding ROC for x(t) = e˜³¹ fτ sin(2t) u(t)dtarrow_forwardcircuit analysissource transform step by step in the most basic formvo findarrow_forwardCompute the Laplace transform of the following time domain function using only L.T. properties: f(t)=(t-3)eu(t − 2)arrow_forward

Introductory Circuit Analysis (13th Edition)Electrical EngineeringISBN:9780133923605Author:Robert L. BoylestadPublisher:PEARSON

Introductory Circuit Analysis (13th Edition)Electrical EngineeringISBN:9780133923605Author:Robert L. BoylestadPublisher:PEARSON Delmar's Standard Textbook Of ElectricityElectrical EngineeringISBN:9781337900348Author:Stephen L. HermanPublisher:Cengage Learning

Delmar's Standard Textbook Of ElectricityElectrical EngineeringISBN:9781337900348Author:Stephen L. HermanPublisher:Cengage Learning Programmable Logic ControllersElectrical EngineeringISBN:9780073373843Author:Frank D. PetruzellaPublisher:McGraw-Hill Education

Programmable Logic ControllersElectrical EngineeringISBN:9780073373843Author:Frank D. PetruzellaPublisher:McGraw-Hill Education Fundamentals of Electric CircuitsElectrical EngineeringISBN:9780078028229Author:Charles K Alexander, Matthew SadikuPublisher:McGraw-Hill Education

Fundamentals of Electric CircuitsElectrical EngineeringISBN:9780078028229Author:Charles K Alexander, Matthew SadikuPublisher:McGraw-Hill Education Electric Circuits. (11th Edition)Electrical EngineeringISBN:9780134746968Author:James W. Nilsson, Susan RiedelPublisher:PEARSON

Electric Circuits. (11th Edition)Electrical EngineeringISBN:9780134746968Author:James W. Nilsson, Susan RiedelPublisher:PEARSON Engineering ElectromagneticsElectrical EngineeringISBN:9780078028151Author:Hayt, William H. (william Hart), Jr, BUCK, John A.Publisher:Mcgraw-hill Education,

Engineering ElectromagneticsElectrical EngineeringISBN:9780078028151Author:Hayt, William H. (william Hart), Jr, BUCK, John A.Publisher:Mcgraw-hill Education,