COMPUTER SYSTEMS&MOD MSGT/ET SA AC PKG

3rd Edition

ISBN: 9780134671123

Author: Bryant

Publisher: PEARSON

expand_more

expand_more

format_list_bulleted

Textbook Question

Chapter 6, Problem 6.40HW

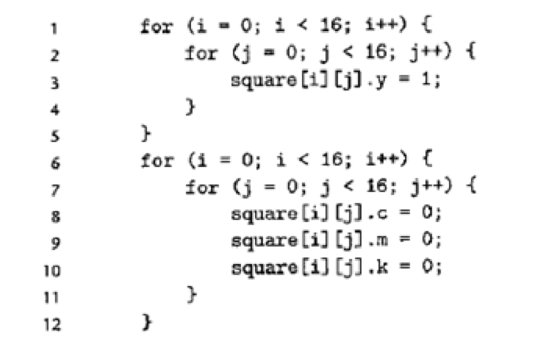

Given the assumptions in Problem 6.38, determine the cache performance of the following code:

- A. What is the total number of writes?

- B. What is the total number of writes that miss in the cache?

- C. C What is the miss rate?

Expert Solution & Answer

Want to see the full answer?

Check out a sample textbook solution

Students have asked these similar questions

Unit 1 Assignment 1 – Loops and Methods (25 points)

Task:

You are working for Kean University and given the task of building an Email

Registration System. Your objective is to generate a Kean email ID and temporary

password for every new user. The system will prompt for user information and generate

corresponding credentials. You will develop a complete Java program that consists of

the following modules:

Instructions:

1. Main Method:

○ The main method should include a loop (of your choice) that asks for input

from five users.

For each user, you will prompt for their first name and last name and

generate the email and password by calling two separate methods.

Example

о Enter your first name: Joe

Enter your last name: Rowling

2.generateEmail() Method:

This method will take the user's first and last name as parameters and return the

corresponding Kean University email address.

The format of the email is:

•

First letter of the first name (lowercase) + Full last name (lowercase) +…

I have attached my code, under I want you to show me how to enhance it and make it more cooler and better in graphics with following the instructions.

Using R language

Chapter 6 Solutions

COMPUTER SYSTEMS&MOD MSGT/ET SA AC PKG

Ch. 6.1 - Prob. 6.1PPCh. 6.1 - Prob. 6.2PPCh. 6.1 - Prob. 6.3PPCh. 6.1 - Prob. 6.4PPCh. 6.1 - Prob. 6.5PPCh. 6.1 - Prob. 6.6PPCh. 6.2 - Prob. 6.7PPCh. 6.2 - Prob. 6.8PPCh. 6.4 - Prob. 6.9PPCh. 6.4 - Prob. 6.10PP

Ch. 6.4 - Prob. 6.11PPCh. 6.4 - Prob. 6.12PPCh. 6.4 - Prob. 6.13PPCh. 6.4 - Prob. 6.14PPCh. 6.4 - Prob. 6.15PPCh. 6.4 - Prob. 6.16PPCh. 6.5 - Prob. 6.17PPCh. 6.5 - Prob. 6.18PPCh. 6.5 - Prob. 6.19PPCh. 6.5 - Prob. 6.20PPCh. 6.6 - Prob. 6.21PPCh. 6 - Prob. 6.22HWCh. 6 - Prob. 6.23HWCh. 6 - Suppose that a 2 MB file consisting of 512-byte...Ch. 6 - The following table gives the parameters for a...Ch. 6 - The following table gives the parameters for a...Ch. 6 - Prob. 6.27HWCh. 6 - This problem concerns the cache in Practice...Ch. 6 - Suppose we have a system with the following...Ch. 6 - Suppose we have a system with following...Ch. 6 - Suppose that a program using the cache in Problem...Ch. 6 - Repeat Problem 6.31 for memory address0x16E8 A....Ch. 6 - Prob. 6.33HWCh. 6 - Prob. 6.34HWCh. 6 - Prob. 6.35HWCh. 6 - Prob. 6.36HWCh. 6 - Prob. 6.37HWCh. 6 - Prob. 6.38HWCh. 6 - Prob. 6.39HWCh. 6 - Given the assumptions in Problem 6.38, determine...Ch. 6 - You are writing a new 3D game that you hope will...Ch. 6 - Prob. 6.42HWCh. 6 - Prob. 6.43HWCh. 6 - Prob. 6.45HWCh. 6 - Prob. 6.46HW

Additional Engineering Textbook Solutions

Find more solutions based on key concepts

If P = 15 kN, determine the average shear stress in the pins at A, B, and C. All pins are in double shear, and ...

Mechanics of Materials (10th Edition)

This optional Google account security feature sends you a message with a code that you must enter, in addition ...

SURVEY OF OPERATING SYSTEMS

Write a function void switchEnds(int array, int size); that is passed the address of the beginning of an array ...

Starting Out with C++: Early Objects (9th Edition)

Describe in general how youd remove any continue statement from a loop in a program and replace it with some st...

Java How to Program, Early Objects (11th Edition) (Deitel: How to Program)

Modify the code you wrote in Question 18 so it adds all of the numbers read from the file and displays their to...

Starting Out with Java: From Control Structures through Data Structures (4th Edition) (What's New in Computer Science)

In Exercises 61 through 66, rewrite the statements using augmented assignment operators. Assume that each varia...

Introduction To Programming Using Visual Basic (11th Edition)

Knowledge Booster

Learn more about

Need a deep-dive on the concept behind this application? Look no further. Learn more about this topic, computer-science and related others by exploring similar questions and additional content below.Similar questions

- Using R languagearrow_forward(Using R language)arrow_forwardAfter our initial deployment for our ML home based security system, the first steps we took to contribute further to the project, we conducted load testing, tested and optimize for low latency, and automated user onboarding. What should be next?arrow_forward

- Why investing in skills and technology is a critical factor in the financial management aspect of system projects.arrow_forwardwhy investing in skills and technology is a critical factor in the financial management aspect of systems projects.arrow_forwardWhy are requirements changing a significant source of risks in system projects?arrow_forward

arrow_back_ios

SEE MORE QUESTIONS

arrow_forward_ios

Recommended textbooks for you

Systems ArchitectureComputer ScienceISBN:9781305080195Author:Stephen D. BurdPublisher:Cengage Learning

Systems ArchitectureComputer ScienceISBN:9781305080195Author:Stephen D. BurdPublisher:Cengage Learning C++ for Engineers and ScientistsComputer ScienceISBN:9781133187844Author:Bronson, Gary J.Publisher:Course Technology Ptr

C++ for Engineers and ScientistsComputer ScienceISBN:9781133187844Author:Bronson, Gary J.Publisher:Course Technology Ptr Microsoft Visual C#Computer ScienceISBN:9781337102100Author:Joyce, Farrell.Publisher:Cengage Learning,

Microsoft Visual C#Computer ScienceISBN:9781337102100Author:Joyce, Farrell.Publisher:Cengage Learning, C++ Programming: From Problem Analysis to Program...Computer ScienceISBN:9781337102087Author:D. S. MalikPublisher:Cengage Learning

C++ Programming: From Problem Analysis to Program...Computer ScienceISBN:9781337102087Author:D. S. MalikPublisher:Cengage Learning Operations Research : Applications and AlgorithmsComputer ScienceISBN:9780534380588Author:Wayne L. WinstonPublisher:Brooks Cole

Operations Research : Applications and AlgorithmsComputer ScienceISBN:9780534380588Author:Wayne L. WinstonPublisher:Brooks Cole EBK JAVA PROGRAMMINGComputer ScienceISBN:9781337671385Author:FARRELLPublisher:CENGAGE LEARNING - CONSIGNMENT

EBK JAVA PROGRAMMINGComputer ScienceISBN:9781337671385Author:FARRELLPublisher:CENGAGE LEARNING - CONSIGNMENT

Systems Architecture

Computer Science

ISBN:9781305080195

Author:Stephen D. Burd

Publisher:Cengage Learning

C++ for Engineers and Scientists

Computer Science

ISBN:9781133187844

Author:Bronson, Gary J.

Publisher:Course Technology Ptr

Microsoft Visual C#

Computer Science

ISBN:9781337102100

Author:Joyce, Farrell.

Publisher:Cengage Learning,

C++ Programming: From Problem Analysis to Program...

Computer Science

ISBN:9781337102087

Author:D. S. Malik

Publisher:Cengage Learning

Operations Research : Applications and Algorithms

Computer Science

ISBN:9780534380588

Author:Wayne L. Winston

Publisher:Brooks Cole

EBK JAVA PROGRAMMING

Computer Science

ISBN:9781337671385

Author:FARRELL

Publisher:CENGAGE LEARNING - CONSIGNMENT

Instruction Format (With reference to address); Author: ChiragBhalodia;https://www.youtube.com/watch?v=lNdy8HREvgo;License: Standard YouTube License, CC-BY