In a pure capacitive circuit, does the current lead or lag the voltage?

Whether the current leads or lags the voltage in a pure capacitive circuit.

Answer to Problem 1RQ

In a pure capacitive circuit, the current leads the applied voltage by .

Explanation of Solution

Description:

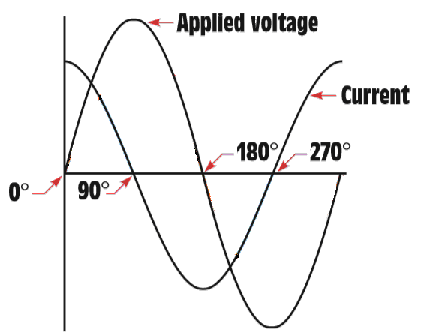

As can be seen from the above figure,

At 0°, value for the applied voltage is zero, while the graph for current is at its positive peak.

At 90°, value for the applied voltage is at its positive peak , while the graph for current is at zero.

At 180°, value for the applied voltage is zero, while the graph for current reaches negative peak.

At 270°, value for the applied voltage reaches negative peak, while the graph for current rises towards zero from the negative peak.

From the above pattern it can be interpreted that current leads the applied voltage by in pure capacitive circuit.

Want to see more full solutions like this?

Chapter 22 Solutions

Delmar's Standard Textbook of Electricity (MindTap Course List)

- I need help on this question a) Find y(t) =yh(t) +yp(t) in time domainIs the system over-damped, under-damped, or critical?arrow_forwardGiven f(t)=a sin(ßt) a = 10 & ß = 23 Find the Laplace Transform using the definition F(s) = ∫f(t)e-stdtarrow_forward= Calculate Avf, Zif, and Zof for the amplifier circuit,Assume he = 50, hie 1.1k2, and identical transistors? 150kQ Vs 5002 HH +25v 10k +6 · 47ΚΩ 47k2 4.7k0} 33 ΚΩ 4.7ΚΩ 10k w 4.7kQ HH Voarrow_forward

- For the four-pole filter in Fig. (2), determine the capacitance values required to produce a critical frequency of 2680 Hz if all the resistors in the RC low-pass circuits are 1.8 K. Also select values for the feedback resistors to get a Butterworth response. Note: For a Butterworth response, the damping factor must be 1.848 for the first stage and 0.765 for the second stage. (2) Re Res ww " = 11arrow_forwardFor the circuit shown in Fig. 2.20, the transistors are identica' and have the following parameters: hje=50, hie = 1.1K, hr =0, and hoe = 0. Calculate Auf, Rif and Rof. Ans: 45.4; 112 KN; 129N. HH 150k 47k R 25 V 10k 47k 4.7k 5μF 33k 4.7k 50µF 50µF 4.7k 4.7k R₁ Roj R1000arrow_forwardA triangular wave is applied to the input of Fig. (3). Determine what the output should be and sketch its waveform in relation to the input. 10μs. 0 5μs 15 μs 0.001 μF R₁ w 2.2karrow_forward

- A three-phase, 480-V, 60-Hz, 6-pole, Y-connected induction motor has its speed controlled by slip power. The circuit parameters are given: Rs=0.06 ohms, Rr=0.05 ohms, Xs=0.2 ohms, Xr=0.3 ohms and Xm=6 ohms. The turn ratio of the rotor to stator winding is n=0.8. The no-load losses of the motor are equal to 150 W. The rotor and stator cupper losses are equal to 249.21 W. The slip power losses are estimated to 8000W. The load torque is 173.61 N.m. at 700 rpm. The efficiency is equal to: Select one: a. 71.5% b. None of these c. 81.5% d. 91.5% Question 2 Consider a 3-phase, 460-V, 100-hp, 0.88 power factor lagging, 4-pole, 1728 RPM, 60 Hz, Y-connected induction motor. The operating slip is equal to: Select one: a. 0.05 b. 0.01 c. 0.04 d. None of these Question 3 A 3 phase, 10 kW, 1750 rpm, Y- connected 460 V, 60 Hz, 4 poles, Y-connected induction motor has the following parameters: Rs = 0.5 Ohms, Rr = 0.3 Ohms, Xs = 0.9 Ohms, Xr = 0.9 Ohms, Xm = 25 Ohms. The no load…arrow_forwardelectric plants do for hand writingarrow_forwardA lighting load of 600 kW and a motor load of 707 kW at 0.707 p.f lagging are supplied by two alternators running in parallel. One machine supplies 900 kW at 0.9 p.f lagging. Find the load sharing and p.f of second machine?arrow_forward

Delmar's Standard Textbook Of ElectricityElectrical EngineeringISBN:9781337900348Author:Stephen L. HermanPublisher:Cengage Learning

Delmar's Standard Textbook Of ElectricityElectrical EngineeringISBN:9781337900348Author:Stephen L. HermanPublisher:Cengage Learning