The CPU we are talking about today is intel core i7- 8750H write in detail about the below given contents for the above CPU Content: specifications about the ISA, including: (a) reduced instruction set computer (RISC), or complex instruction set computing (CISC), b) number of instructions, (c) number and type of memory addressing modes, (d) number of operands per instructions, (e) operand escape patterns (if applicable), (f) “interesting” instructions, such as autoincrementing, different data size

The CPU we are talking about today is intel core i7- 8750H

write in detail about the below given contents for the above CPU

Content:

specifications about the ISA, including:

(a) reduced instruction set computer (RISC), or complex instruction set computing (CISC),

b) number of instructions,

(c) number and type of memory addressing modes,

(d) number of operands per instructions,

(e) operand escape patterns (if applicable),

(f) “interesting” instructions, such as autoincrementing, different data sizes (integer, double, word,etc.), unusual branching constructs, mass data movements. Anything that you think is “interest-ing.”

specifications :

The i7-8750H operates at 2.2 GHz with a TDP of 45 W and a turbo boost of up to 4.1 GHz. This chip integrates Intel's UHD Graphics 630 GPU operating at 350 MHz with a burst frequency of up to 1.1 GHz and supports up to 64 GiB of dual-channel DDR4-2666 memory. This model has a configurable TDP-down of 35 W.

a)x86 CPU's use CISC at instruction/programming level, and RISC-style at execution level.

Since that's most effective way of getting perfrormance out of the code.

Complex Instruction Set Architecture (CISC) –

The main idea is that a single instruction will do all loading, evaluating and storing operations just like a multiplication command will do stuff like loading data, evaluating and storing it, hence it’s complex.

Both approaches try to increase the CPU performance

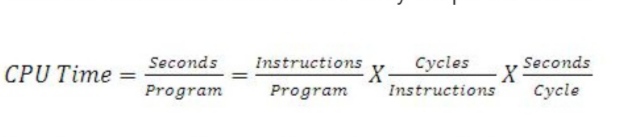

RISC: Reduce the cycles per instruction at the cost of the number of instructions per program.

CISC: The CISC approach attempts to minimize the number of instructions per program but at the cost of an increase in a number of cycles per instruction.

Earlier when programming was done using assembly language, a need was felt to make instruction do more task because programming in assembly was tedious and error-prone due to which CISC architecture evolved but with uprise of high-level language dependency on assembly reduced RISC architecture prevailed.

Characteristic of CISC –

- Complex instruction, hence complex instruction decoding.

- Instruction are larger than one word size.

- Instruction may take more than single clock cycle to get executed.

- Less number of general purpose register as operation get performed in memory itself.

- Complex Addressing Modes.

- More Data types

Trending now

This is a popular solution!

Step by step

Solved in 2 steps with 1 images