7. Assume the 74HC393A counter is operating at 102°C with Vcc=3V. What is the minimum pulse width for the RESET input? O24 ns O 27 ns O 30 ns 36 ns

7. Assume the 74HC393A counter is operating at 102°C with Vcc=3V. What is the minimum pulse width for the RESET input? O24 ns O 27 ns O 30 ns 36 ns

Introductory Circuit Analysis (13th Edition)

13th Edition

ISBN:9780133923605

Author:Robert L. Boylestad

Publisher:Robert L. Boylestad

Chapter1: Introduction

Section: Chapter Questions

Problem 1P: Visit your local library (at school or home) and describe the extent to which it provides literature...

Related questions

Question

PLEASE ANSWER ALL PARTS ASAP!!!!! VERY URGENT!!!!!

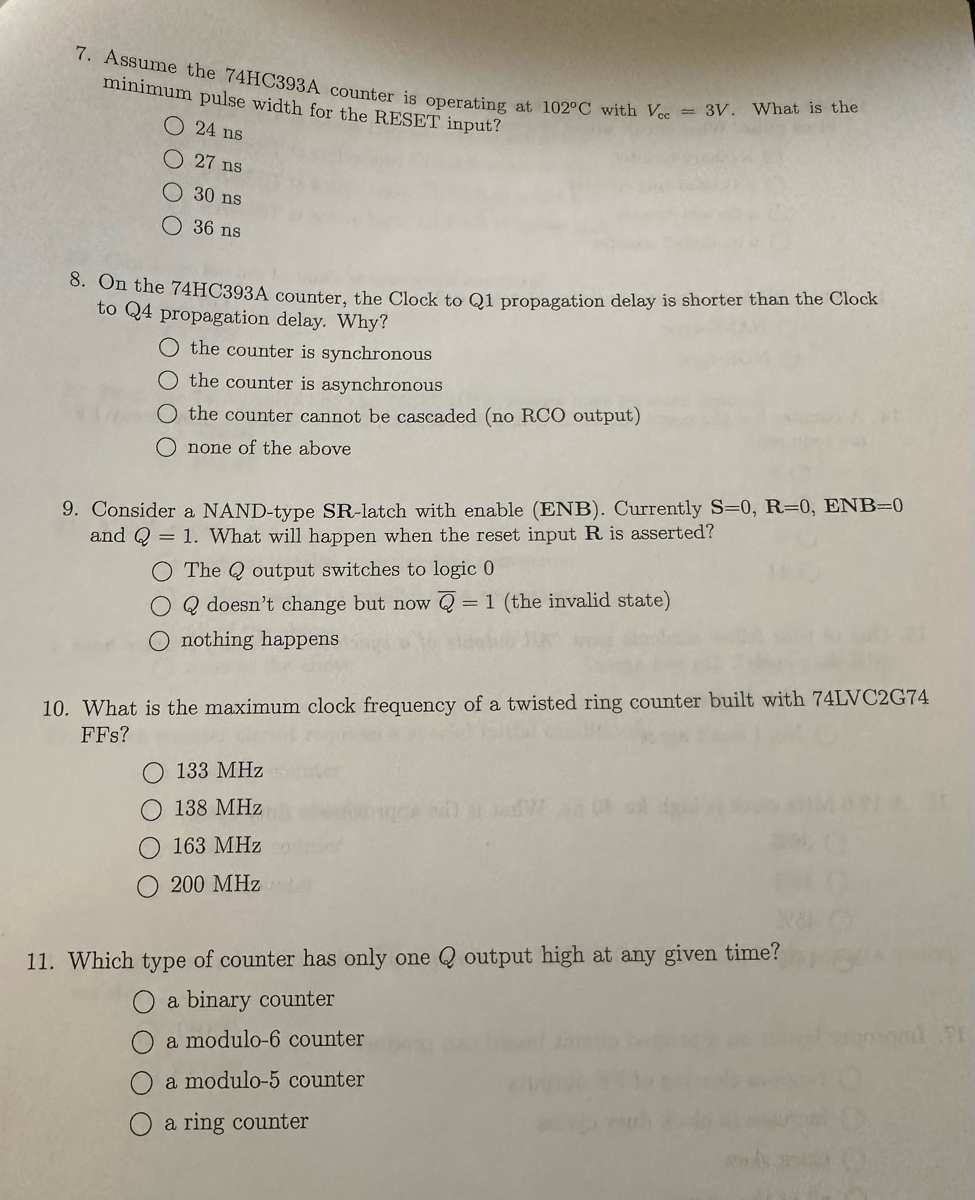

Transcribed Image Text:7. Assume the 74HC393A counter is operating at 102°C with Vcc=3V. What is the

minimum pulse width for the RESET input?

24 ns

27 ns

30 ns

36 ns

8. On the 74HC393A counter, the Clock to Q1 propagation delay is shorter than the Clock

to Q4 propagation delay. Why?

O the counter is synchronous

O the counter is asynchronous

O the counter cannot be cascaded (no RCO output)

O none of the above

9. Consider a NAND-type SR-latch with enable (ENB). Currently S=0, R=0, ENB=0

and Q=1. What will happen when the reset input R is asserted?

O The Qoutput switches to logic 0

O Q doesn't change but now Q = 1 (the invalid state)

O nothing happens

10. What is the maximum clock frequency of a twisted ring counter built with 74LVC2G74

FFs?

133 MHz

138 MHz

163 MHz

200 MHz

11. Which type of counter has only one Qoutput high at any given time?

a binary counter

a modulo-6 counter

a modulo-5 counter

O a ring counter

Expert Solution

Step 1

According to the question,

Step by step

Solved in 3 steps with 4 images

Knowledge Booster

Learn more about

Need a deep-dive on the concept behind this application? Look no further. Learn more about this topic, electrical-engineering and related others by exploring similar questions and additional content below.Recommended textbooks for you

Introductory Circuit Analysis (13th Edition)

Electrical Engineering

ISBN:

9780133923605

Author:

Robert L. Boylestad

Publisher:

PEARSON

Delmar's Standard Textbook Of Electricity

Electrical Engineering

ISBN:

9781337900348

Author:

Stephen L. Herman

Publisher:

Cengage Learning

Programmable Logic Controllers

Electrical Engineering

ISBN:

9780073373843

Author:

Frank D. Petruzella

Publisher:

McGraw-Hill Education

Introductory Circuit Analysis (13th Edition)

Electrical Engineering

ISBN:

9780133923605

Author:

Robert L. Boylestad

Publisher:

PEARSON

Delmar's Standard Textbook Of Electricity

Electrical Engineering

ISBN:

9781337900348

Author:

Stephen L. Herman

Publisher:

Cengage Learning

Programmable Logic Controllers

Electrical Engineering

ISBN:

9780073373843

Author:

Frank D. Petruzella

Publisher:

McGraw-Hill Education

Fundamentals of Electric Circuits

Electrical Engineering

ISBN:

9780078028229

Author:

Charles K Alexander, Matthew Sadiku

Publisher:

McGraw-Hill Education

Electric Circuits. (11th Edition)

Electrical Engineering

ISBN:

9780134746968

Author:

James W. Nilsson, Susan Riedel

Publisher:

PEARSON

Engineering Electromagnetics

Electrical Engineering

ISBN:

9780078028151

Author:

Hayt, William H. (william Hart), Jr, BUCK, John A.

Publisher:

Mcgraw-hill Education,