(a)

Show that the given circuit satisfies Kirchhoff’s current law at junction terminals x-y.

(a)

Answer to Problem 1P

Yes, the given circuit satisfies Kirchhoff’s current law at junction terminals x-y.

Explanation of Solution

Given data:

Refer to Figure given in the textbook.

The voltage delivered by the source is

PSPICE Simulation:

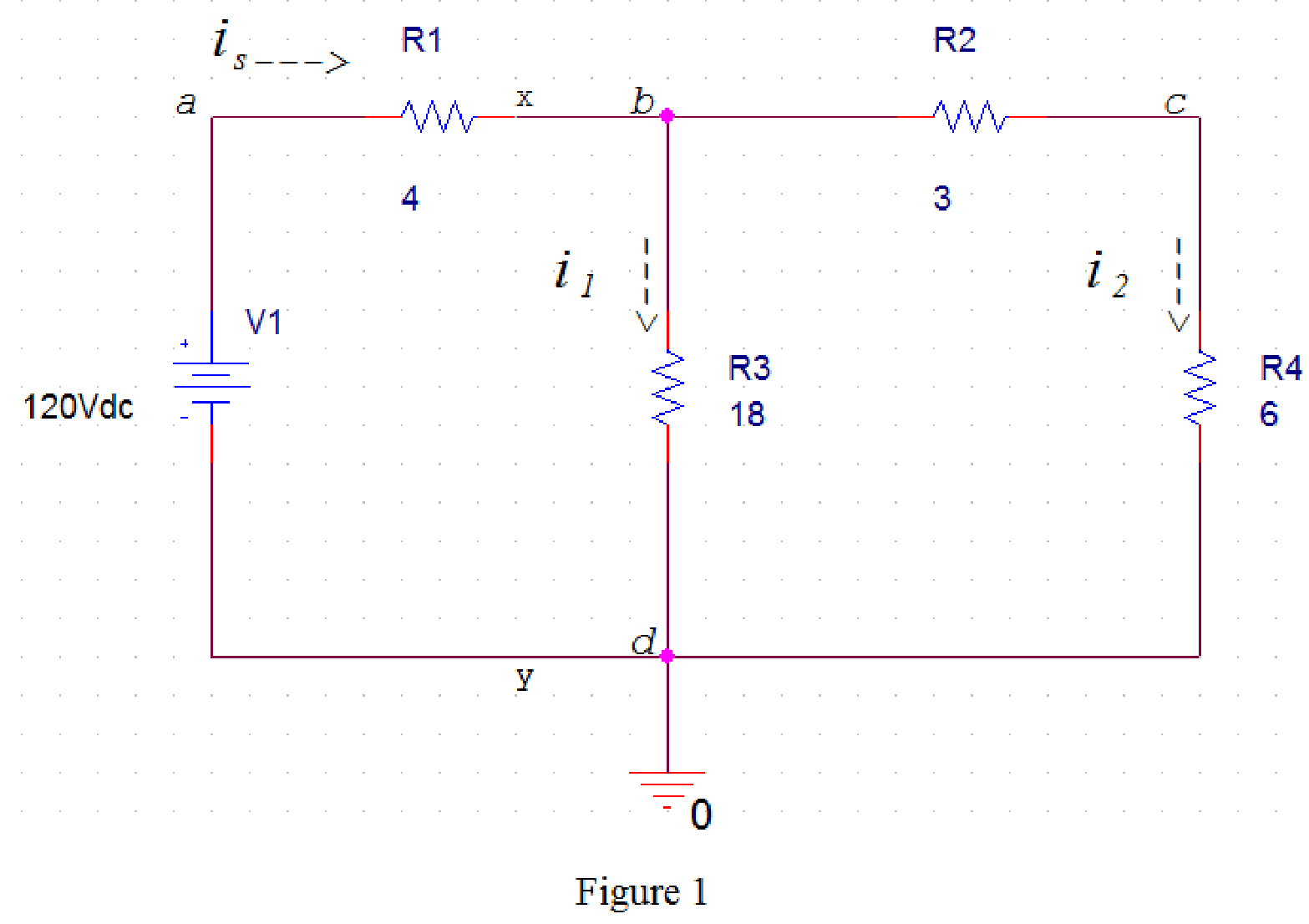

Draw the circuit diagram in PSpice as shown in Figure 1.

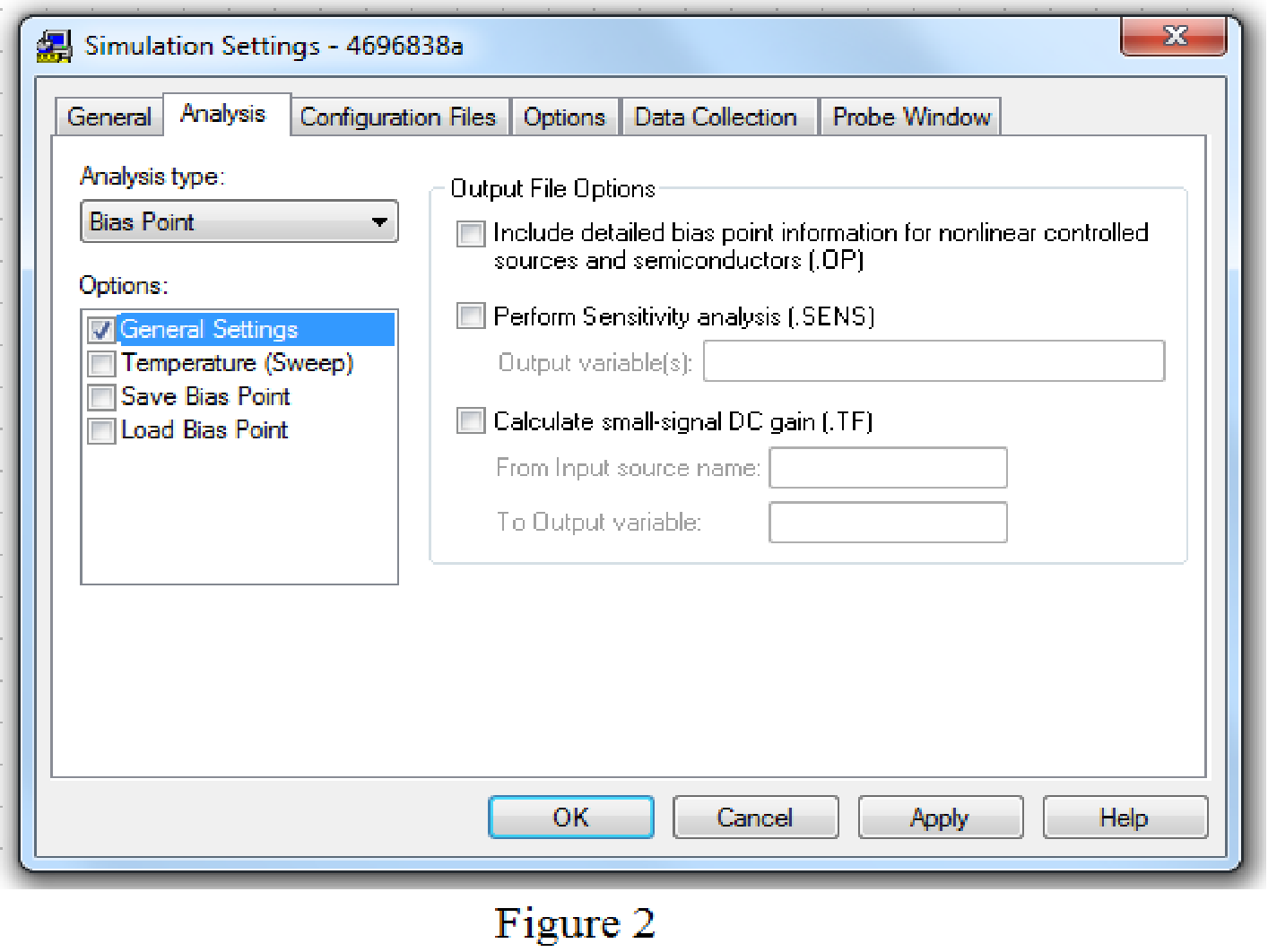

Save the circuit and provide the Simulation Settings as shown in Figure 2.

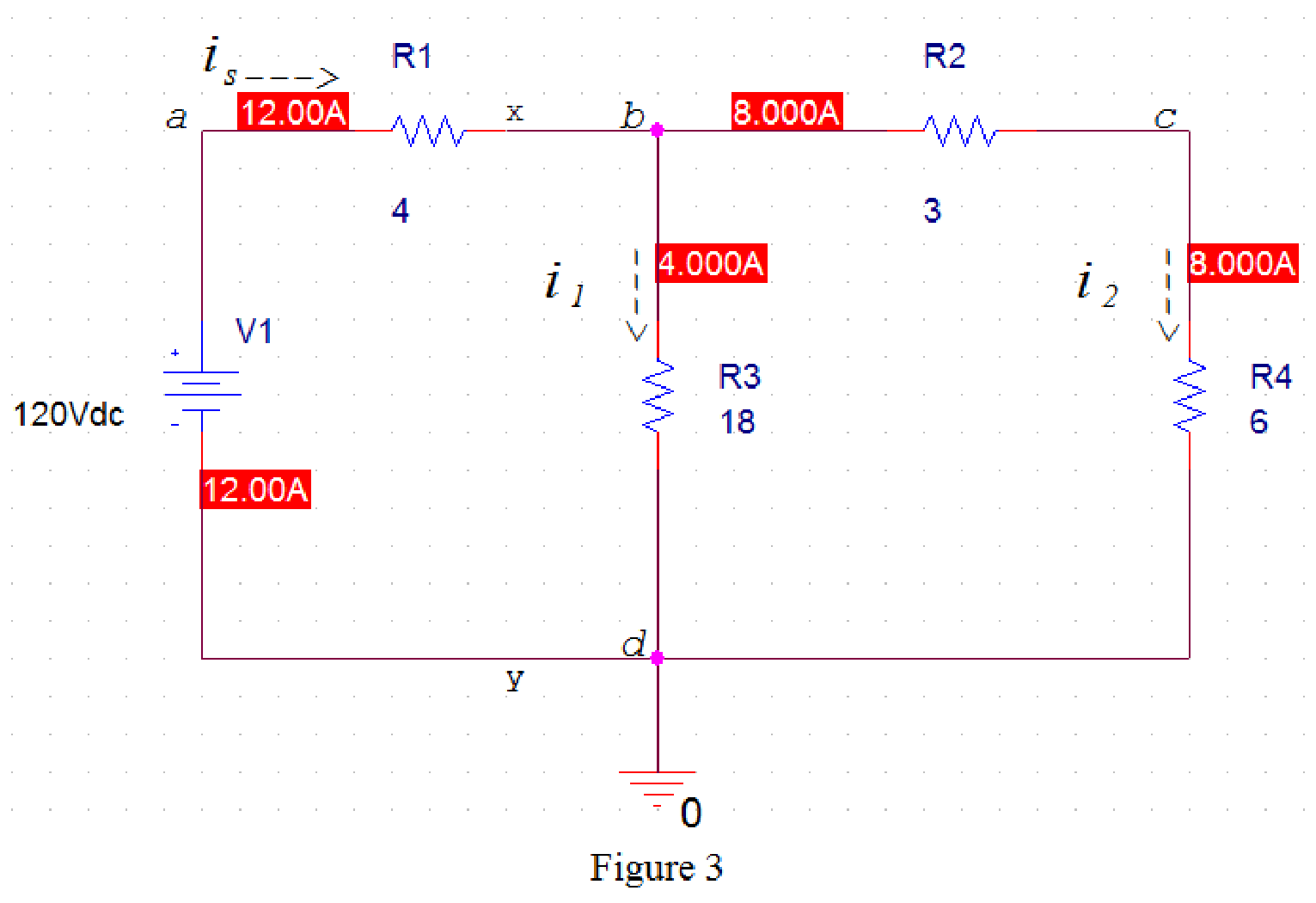

Now run the simulation and the results will be displayed as shown in Figure 3 by enabling the “Enable Bias Current Display” icon.

From Figure 3, source current

Kirchhoff’s current law states that the current entering the node is equal to the current leaving the node.

In Figure 3, apply Kirchhoff current law at node b. Therefore,

Rearrange the equation (1) as follows,

Substitute

Hence, the given circuit satisfies Kirchhoff’s current law at junction terminals x-y.

Conclusion:

Thus, yes, the given circuit satisfies Kirchhoff’s current law at junction terminals x-y.

(b)

Show that the given circuit satisfies Kirchhoff’s voltage law.

(b)

Answer to Problem 1P

Yes, the given circuit satisfies Kirchhoff’s voltage law.

Explanation of Solution

Given data:

Refer to Figure given in the textbook.

Voltage delivered by the source is

PSPICE Simulation:

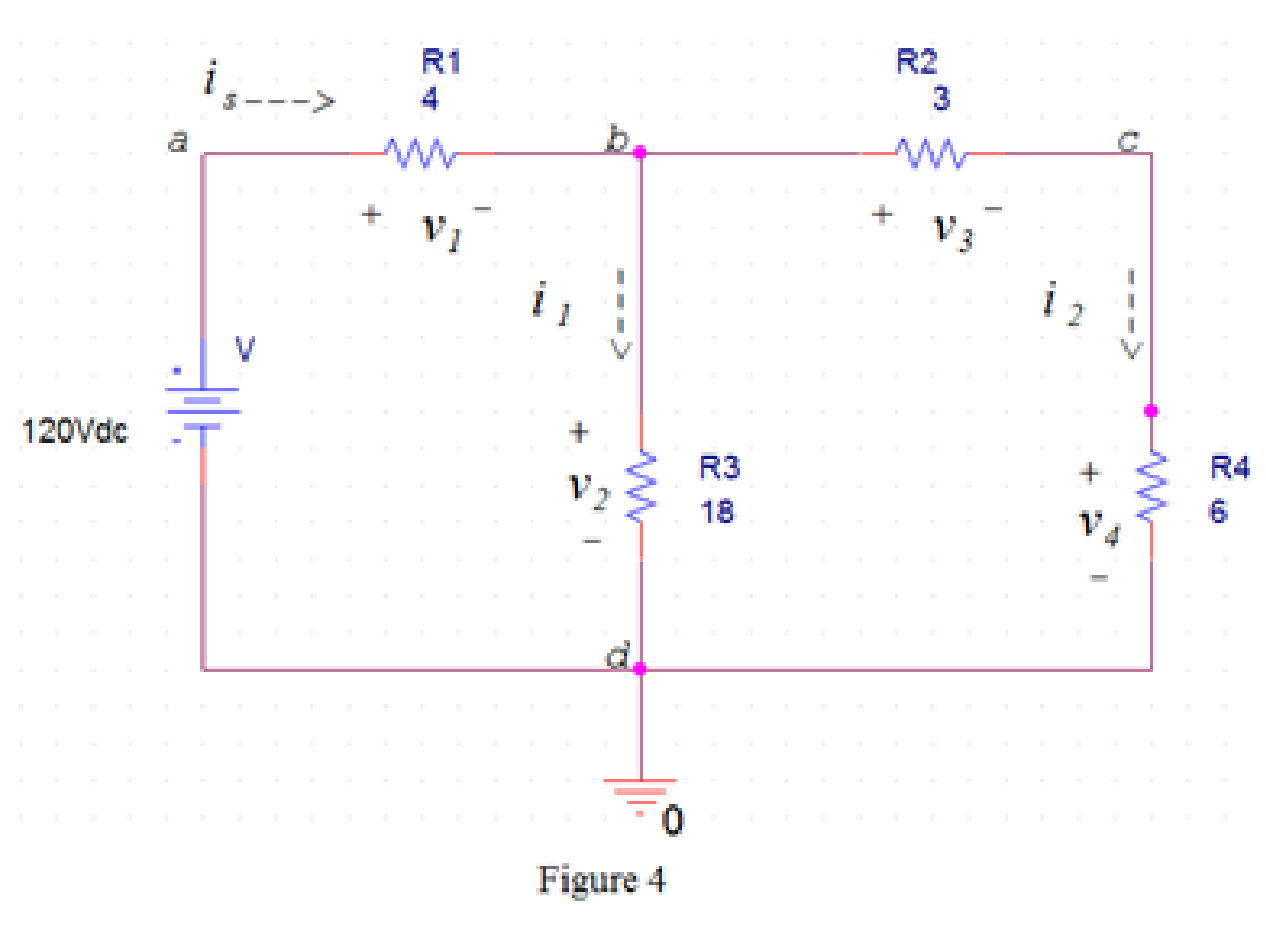

Draw the circuit diagram in PSpice as shown in Figure 4.

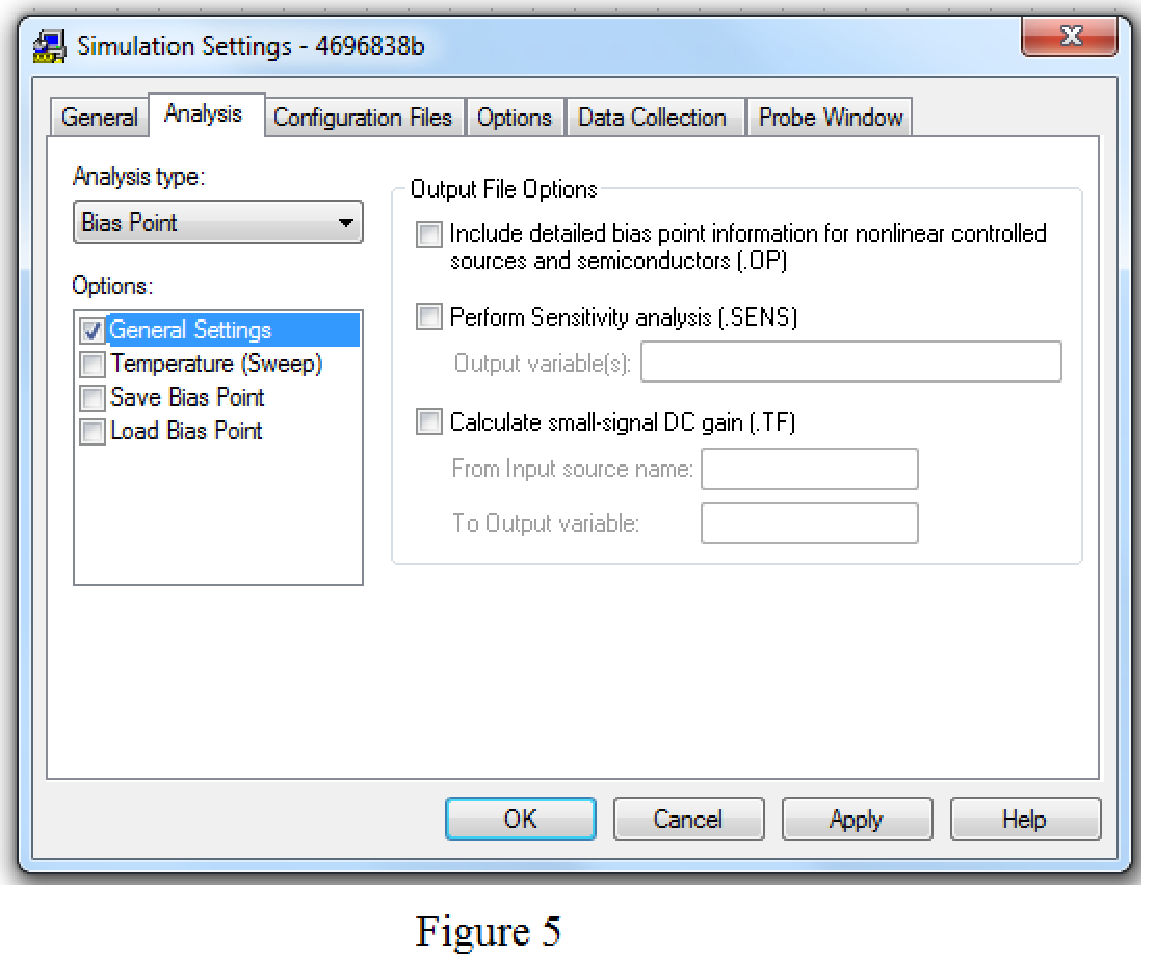

Save the circuit and provide the Simulation Settings as shown in Figure 5.

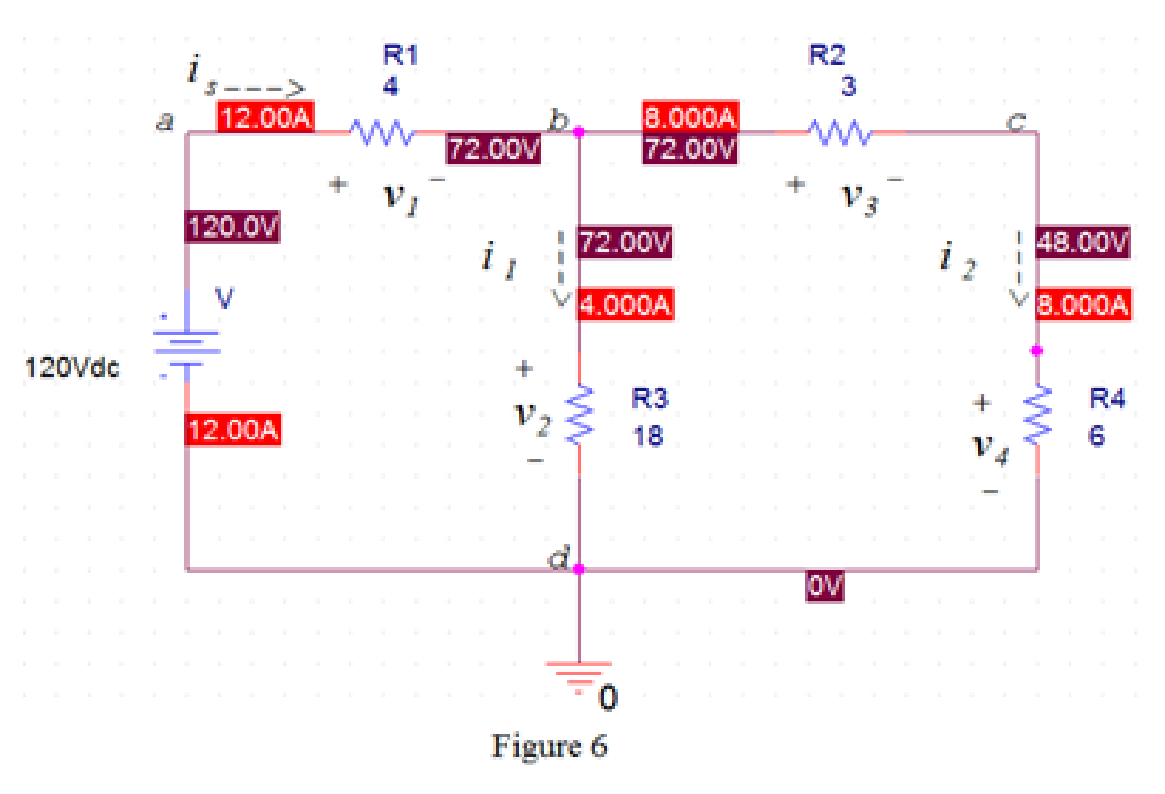

Now run the simulation and the results will be displayed as shown in Figure 3 by enabling the “Enable Bias Current Display” icon and “Enable Bias Voltage Display” icon.

From Figure 6, the voltage

The voltage

The voltage

The voltage

Kirchhoff’s voltage law states that the sum of the voltage rise around any closed loop must be equal to the sum of voltage drops around that loop.

In Figure 6, apply Kirchhoff’s voltage law to the loop abda.

From Figure 6, the source voltage

Substitute

In Figure 6, apply Kirchhoff’s voltage law to the loop bcdb.

Substitute

In Figure 6, apply Kirchhoff’s voltage law to the loop abcda.

Substitute

Hence, the given circuit satisfies Kirchhoff’s voltage law around every closed loop.

Conclusion:

Thus, yes, the given circuit satisfies Kirchhoff’s voltage law.

Want to see more full solutions like this?

Chapter 3 Solutions

Electric Circuits (10th Edition)

- Q2. a) Two three-phase transformers, designated A and B, have the following secondary equivalent circuit parameters per phase: R₁ = 0.002 Q, XA = 0.03 Q, RB = 0.004 Q, X = 0.012 Q Transformer A is 250 kVA and transformer B is 450 kVA. Calculate how they share a load of 650 KVA when connected in parallel (assume the voltage ratios are equal) b) A step-up transformer is being specified for the beginning of a 3-phase, 4 wire high voltage transmission line. Discuss your recommendation for the configuration of the transformer connections on both the primary and secondary side of the transformer. c) Define power system protection and describe its fundamental purpose. Discuss the following key concepts including discrimination, stability, speed of operation, sensitivity, and reliability in the context of the power system protection components and schemes.arrow_forwardQ3. a) Given the unsymmetrical phasors for a three-phase system, they can be represented in terms of their symmetrical components as follows: [Fa] [1 1 Fb = 1 a² [Fc. 11[Fao] a Fai 1 a a2F a2- where F stands for any three-phase quantity. Conversely, the sequence components can be derived from the unsymmetrical phasors as: [11 1] [Fal Faol Fa1 = 1 a a² F 1 a² a a2. Given the unbalanced three-phase voltages: V₁ = 120/10° V, V₂ = 200/110° V, V = 240/200° V Calculate in polar form the sequence components of the voltage.arrow_forwardComplete the table of values for this circuit:arrow_forward

- *P2.58. Solve for the node voltages shown in Figure P2.58. - 10 Ω w + 10 Ω 15 Ω w w '+' 5 Ω 20x 1 A Figure P2.58 w V2 502 12Aarrow_forwardAn 18.65 kW, 4-pole, 50 Hz, 3-phase induction motor has friction and windage losses of 2.5% of the output. The full-load slip is 4%. Find for full-load (i) the rotor cu loss (ii) the rotor input power (iii) the output torque.arrow_forwardQ1: Consider the finite state machine logic implementation in Fig. shown below: a. b. Construct the state diagram. Repeat the circuit design using j-k flip flop. C'lk A D 10 Clk Q D 32 Cik O 31 Please solve the question on a sheet of paper by hand and explain everything related to the question step by step.arrow_forward

- Anot ined sove in peaper S PU +96 An 18.65 kW, 4-pole, 50 Hz, 3-phase induction motor has friction and windage losses of 2.5% of the output. The full-load slip is 4 %. Find for full-load (i) the rotor cu loss (ii) the rotor input power (iii) the output torque. 750 1 T el Marrow_forwardAlternator has star-connected,4-pole, 50 Hz as the following data: Flux per pole-0.12 Wb; No. of slot/pole/phase=4; conductor/slot=4; Each coil spans 150° (electrical degree) pitches Find (i) number of turns per phase (ii) distribution factor (iii) pitch factor (iv) no-load phase voltage (v) no-load line voltage.arrow_forwardAlternator has star-connected,4-pole, 50 Hz as the following data: Flux per pole-0.12 Wb; No. of slot/pole/phase=4; conductor/slot=4; Each coil spans 150° (electrical degree) pitches Find (i) number of turns per phase (ii) distribution factor (iii) pitch factor (iv) no-load phase voltage (v) no-load line voltage.arrow_forward

- A) Suppose you were desiging a circuit that required two LEDs for "power on" indication. The power supply voltage is 5 volts, and each LED is rated at 1.6 volts and 20 mA. Calculate the dropping resistor sizes and power ratings: B) After doing this, a co-worker looks at your circuit and suggests a modification. Why not use a single dropping resistor for both LEDs, economizing the number of components necessary? Re-calculate the dropping resistor ratings (resistance and power) for the new design. Include the total power consumed by the circuit and the power delivered by the source.arrow_forwardS A L ined sove in peaper ۳/۱ 16852 Alternator has star-connected,4-pole, 50 Hz as the following data: Flux per pole-0.12 Wb; No. of slot/pole/phase-4; conductor/slot-4; Each coil spans 150° (electrical degree) pitches Find (i) number of turns per phase (ii) distribution factor (iii) pitch factor (iv) no-load phase voltage (v) no-load line voltage. 2ci25 750 r 2.01 ४arrow_forwardA) Complete the table of values for this circuit: B) Draw the schematic include polarityarrow_forward

Introductory Circuit Analysis (13th Edition)Electrical EngineeringISBN:9780133923605Author:Robert L. BoylestadPublisher:PEARSON

Introductory Circuit Analysis (13th Edition)Electrical EngineeringISBN:9780133923605Author:Robert L. BoylestadPublisher:PEARSON Delmar's Standard Textbook Of ElectricityElectrical EngineeringISBN:9781337900348Author:Stephen L. HermanPublisher:Cengage Learning

Delmar's Standard Textbook Of ElectricityElectrical EngineeringISBN:9781337900348Author:Stephen L. HermanPublisher:Cengage Learning Programmable Logic ControllersElectrical EngineeringISBN:9780073373843Author:Frank D. PetruzellaPublisher:McGraw-Hill Education

Programmable Logic ControllersElectrical EngineeringISBN:9780073373843Author:Frank D. PetruzellaPublisher:McGraw-Hill Education Fundamentals of Electric CircuitsElectrical EngineeringISBN:9780078028229Author:Charles K Alexander, Matthew SadikuPublisher:McGraw-Hill Education

Fundamentals of Electric CircuitsElectrical EngineeringISBN:9780078028229Author:Charles K Alexander, Matthew SadikuPublisher:McGraw-Hill Education Electric Circuits. (11th Edition)Electrical EngineeringISBN:9780134746968Author:James W. Nilsson, Susan RiedelPublisher:PEARSON

Electric Circuits. (11th Edition)Electrical EngineeringISBN:9780134746968Author:James W. Nilsson, Susan RiedelPublisher:PEARSON Engineering ElectromagneticsElectrical EngineeringISBN:9780078028151Author:Hayt, William H. (william Hart), Jr, BUCK, John A.Publisher:Mcgraw-hill Education,

Engineering ElectromagneticsElectrical EngineeringISBN:9780078028151Author:Hayt, William H. (william Hart), Jr, BUCK, John A.Publisher:Mcgraw-hill Education,