For the logic diagram provided, give the logic expression for the output F. 35ns 25ns 5ns 25ns F-( (A-B-C)' · (B-C')' Y

For the logic diagram provided, give the logic expression for the output F. 35ns 25ns 5ns 25ns F-( (A-B-C)' · (B-C')' Y

Introductory Circuit Analysis (13th Edition)

13th Edition

ISBN:9780133923605

Author:Robert L. Boylestad

Publisher:Robert L. Boylestad

Chapter1: Introduction

Section: Chapter Questions

Problem 1P: Visit your local library (at school or home) and describe the extent to which it provides literature...

Related questions

Question

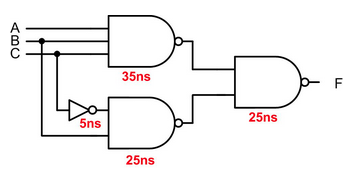

Transcribed Image Text:For the logic diagram provided, determine the logic expression for the output F.

### Logic Diagram

The diagram consists of three logic gates:

1. **AND Gate** (top left):

- Inputs: A, B, C

- Delay: 35 ns

2. **NOT Gate**:

- Input: B

- Output goes into the OR gate and another AND gate

- Delay: 5 ns

3. **AND Gate** (bottom):

- Inputs: B' (output from NOT gate), C

- Delay: 25 ns

4. **OR Gate** (center):

- Inputs: Outputs from the two AND gates

- Delay: 25 ns

- Output: F

### Logic Expression Options

- \( F = (A \cdot B \cdot C') \cdot (B \cdot C)' \)

- \( F = (A' \cdot B' \cdot C' + B' \cdot C)' \)

- \( F = (A \cdot B \cdot C \cdot B' \cdot C')' \)

- \( F = (A \cdot B \cdot C') + (B \cdot C')' \)

### Explanation

Select the correct logic expression based on the diagram and the listed options. The total delay is measured from the path with the greatest cumulative gate delay, which affects the timing performance of the circuit.

Expert Solution

Step 1

Given the circuit diagram:

We need to find the logic expression for the output F.

Step by step

Solved in 2 steps with 2 images

Recommended textbooks for you

Introductory Circuit Analysis (13th Edition)

Electrical Engineering

ISBN:

9780133923605

Author:

Robert L. Boylestad

Publisher:

PEARSON

Delmar's Standard Textbook Of Electricity

Electrical Engineering

ISBN:

9781337900348

Author:

Stephen L. Herman

Publisher:

Cengage Learning

Programmable Logic Controllers

Electrical Engineering

ISBN:

9780073373843

Author:

Frank D. Petruzella

Publisher:

McGraw-Hill Education

Introductory Circuit Analysis (13th Edition)

Electrical Engineering

ISBN:

9780133923605

Author:

Robert L. Boylestad

Publisher:

PEARSON

Delmar's Standard Textbook Of Electricity

Electrical Engineering

ISBN:

9781337900348

Author:

Stephen L. Herman

Publisher:

Cengage Learning

Programmable Logic Controllers

Electrical Engineering

ISBN:

9780073373843

Author:

Frank D. Petruzella

Publisher:

McGraw-Hill Education

Fundamentals of Electric Circuits

Electrical Engineering

ISBN:

9780078028229

Author:

Charles K Alexander, Matthew Sadiku

Publisher:

McGraw-Hill Education

Electric Circuits. (11th Edition)

Electrical Engineering

ISBN:

9780134746968

Author:

James W. Nilsson, Susan Riedel

Publisher:

PEARSON

Engineering Electromagnetics

Electrical Engineering

ISBN:

9780078028151

Author:

Hayt, William H. (william Hart), Jr, BUCK, John A.

Publisher:

Mcgraw-hill Education,